# Cadence® Virtual Component Co-Design Architecture Evaluation Guide

Product Version 2.1 March 2001

© 1998-2001 Cadence Design Systems, Inc. All rights reserved. Printed in the United States of America.

Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134, USA

**Trademarks:** Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 1-800-862-4522.

All other trademarks are the property of their respective holders.

**Restricted Print Permission:** This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used solely for personal, informational, and noncommercial purposes;

- 2. The publication may not be modified in any way;

- 3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and

- 4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

# **Contents**

| Drofoss                                        | _   |

|------------------------------------------------|-----|

| Preface                                        |     |

| Related Documents                              |     |

| Typographic and Syntax Conventions             | . 8 |

|                                                |     |

| <u>1</u>                                       |     |

| <u>Overview</u>                                | . 9 |

| Integration-Based Design Flow                  | 11  |

| Capturing Behavior                             |     |

| Running a Functional Simulation                | 13  |

| Capturing Architecture                         |     |

| Mapping Behavior to Architecture               | 16  |

| Running a Performance Simulation               | 18  |

| Refining Mapping Diagrams                      | 19  |

| Exploration                                    | 20  |

| Derivative Design                              | 20  |

| Hardware/Software Partitioning Changes         | 20  |

| "What If" Scenario                             | 21  |

| 2                                              |     |

|                                                |     |

| Performance Models                             |     |

| Performance Models of Architecture Components  |     |

| Typical Architecture Services                  | 28  |

| Additional Architecture Services               | 32  |

| Behavior Performance on Software Architectures | 32  |

| Execution Delays                               | 32  |

| Delays Based on the Processor                  |     |

| Delays Based on Memory Accesses                | 34  |

| Performance Modeling Styles                    |     |

| DSL Performance Model                          | 36  |

| Annotated C Performance Model                  | 39  |

| Annotated C++ Performance Model                     | 40 |

|-----------------------------------------------------|----|

| Scheduling Shared Resources                         |    |

| Performance Impact of Scheduling                    |    |

| Scheduler Services                                  |    |

| Single-Threaded Scheduling Model                    | 47 |

| RTOS Scheduler Services                             | 48 |

| RTOS Models                                         | 50 |

| Nested Schedulers                                   |    |

|                                                     |    |

| 3                                                   |    |

|                                                     | 55 |

|                                                     |    |

| Bus Arbitration                                     |    |

| Arbitration Models                                  |    |

| Communication Patterns                              |    |

| Performance Model of a Pattern                      |    |

| Additional Services                                 |    |

| Reusability of Patterns                             |    |

| Pattern Support for Fanouts                         |    |

| Addressing                                          |    |

| Behavior Memories                                   |    |

| <u>Using Behavior Memories</u>                      |    |

| Mapping the Memory Instance                         |    |

| DMA Modeling                                        |    |

| Cache Modeling                                      |    |

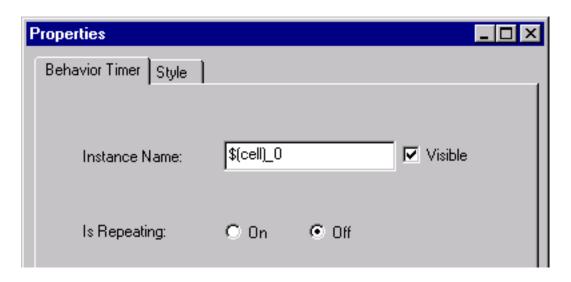

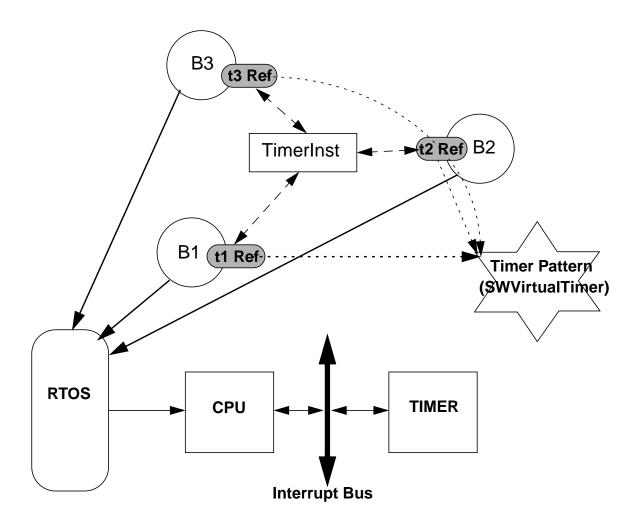

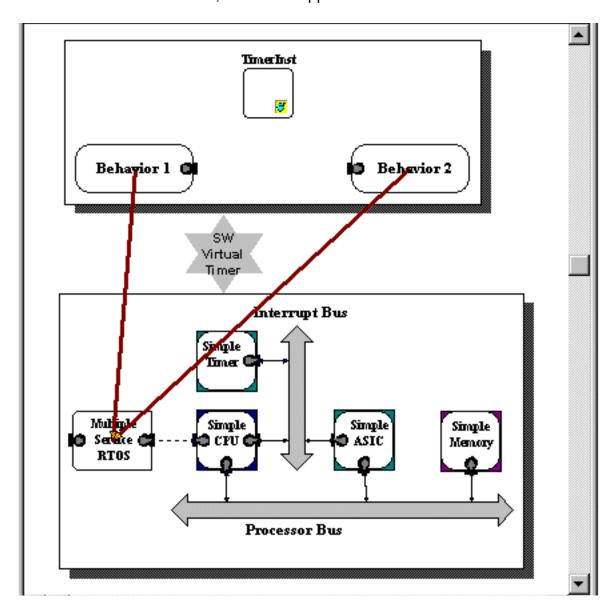

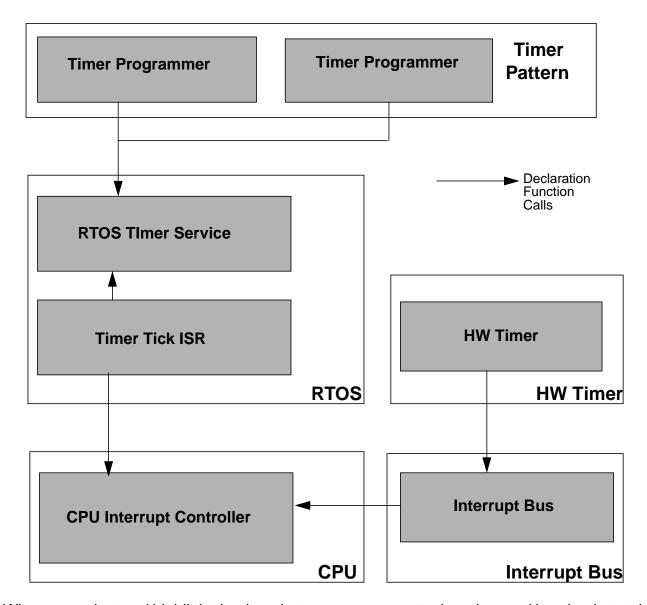

| Behavior Timers                                     |    |

| Place the Timer Instance                            |    |

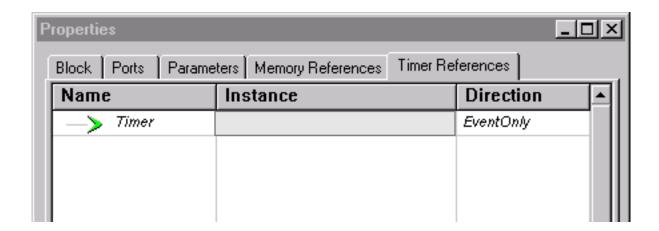

| Declare the Timer Reference                         |    |

| Associating a Timer Reference with a Timer Instance |    |

| Interacting with the Timer from within Your Model   |    |

| Mapping the Timer                                   | 91 |

|                                                     |    |

| <u>4</u>                                            |    |

| Analyzing Behavior Delay                            | 97 |

| Creating the Mapping Diagram                        |    |

| Mapping Configurations                              |    |

| <del></del>                                         |    |

| Analyzing the Behavior Delay of a Hardware/Software Partition | . 99 |

|---------------------------------------------------------------|------|

| General Mapping Guidelines                                    |      |

| Using the Performance Viewlist                                |      |

| Binding Performance Models Explicitly                         |      |

| Mapping Parameters                                            |      |

| Analyzing Bus Traffic                                         | 102  |

| Refining Communication Patterns                               | 106  |

| Pattern Categories                                            | 107  |

| Pattern Defaults                                              | 108  |

| Mapping Parameters                                            | 109  |

| Performance Analysis of Patterns                              | 109  |

| Analyzing Memory Access                                       | 109  |

| Instruction and Data Fetch Analysis                           | 110  |

| Performance Analysis of Behavior Memories                     | 110  |

| Cache Analysis                                                |      |

| Analyzing Timer Accesses                                      | 117  |

| 5 Performance Evaluation                                      | 119  |

| Simulating the Mapping Diagram                                | 119  |

| Setting Up the Simulation                                     |      |

| Initializing and Running the Simulation                       |      |

| Debugging Simulation Problems                                 |      |

| Exploring the Mapping Diagram                                 |      |

| Exporting Parameters                                          |      |

| Sweeping Parameters                                           |      |

| Analyzing Simulation Results                                  |      |

| Using Model Viewports                                         | 127  |

| Simulation Messages                                           | 131  |

| Comparing Functional and Performance Simulation Results       | 131  |

| Analyzing Testbench Results                                   |      |

| Analyzing Table Charts                                        | 132  |

| Analyzing Gantt Charts                                        | 132  |

| <u>6</u><br>Mapping Refinement                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protocol Down Converter Refinement 139  Creating a Refinement Model 149  Instantiating and Mapping a Refinement 149  Simulating and Analyzing a Refinement 149  Specifying a Sub-Configuration for a Refinement 149 |

| A Pattern Descriptions Software-to-Hardware Communication Hardware-to-Hardware Communication Hardware-to-Software Communication 153                                                                                 |

| Software-to-Software Communication                                                                                                                                                                                  |

# **Preface**

This manual describes how to customize output from the Cadence® Virtual Component Co-Design (VCC) environment for use with a software debugger or a co-verification tool. You customize output from the VCC environment by writing extensions to the Links to Implementation feature in VCC.

This manual shows how to extend Links to Implementation so that it generates

- Probes for software debuggers that the VCC environment does not already support

- Startup and configuration files for co-verification tools that the VCC environment does not already support

This manual is for design flow engineers who integrate third-party tools into the VCC design flow at the customer site for use by system designers and virtual component providers.

The preface discusses

- Related Documents on page 7

- <u>Typographic and Syntax Conventions</u> on page 8

# **Related Documents**

The following documents give you more information about the VCC environment and related applications.

| For information about                                                                                | Refer to                                                                                                                                        |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| How to accomplish specific tasks in the VCC environment and what each menu command does              | Help Topics: Cadence Virtual Component Co-Design (to open VCC Help, start the Create editor and choose the Help > VCC Help Topics menu command) |

| Modeling behavior, architecture, and implementation; strategies for capturing and verifying behavior | VCC Modeling Guide                                                                                                                              |

### Preface

| For information about                                                                           | Refer to                                                 |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| The design libraries in the Project Folder                                                      | VCC Library Reference                                    |

| Exporting hardware and software for coverification; importing cycle-accurate simulation results | VCC Links to Implementation Design Guide                 |

| Customizing VCC output for use with a debugger or a co-verifier                                 | VCC Links to Implementation Flow<br>Customization Guide  |

| Creating SPW models, which you can import into the VCC environment                              | Signal Processing WorkSystem (SPW) documentation library |

# **Typographic and Syntax Conventions**

This manual uses the following typographic and syntax conventions.

■ Text that you type, such as commands, filenames, and values for dialog box fields, appears in Courier type.

**Example:** Type create to start the Create editor from a UNIX window.

Variables appear in Courier italic type.

**Example:** 1ib.cell:view defines the library, cell, and view for each model in the Project Folder.

■ User interface elements, such as field names, button names, menus, menu commands, and items in clickable list boxes, appear in Helvetica italic type.

**Example:** From the *Edit* menu, choose the *Data Types* command.

Menu commands use the > character to indicate menu levels.

**Example:** Choose the *Edit > Data Types* command.

A Caution informs you about possible damage to equipment, data, or software.

/Important

An Important emphasizes valuable information.

# **Overview**

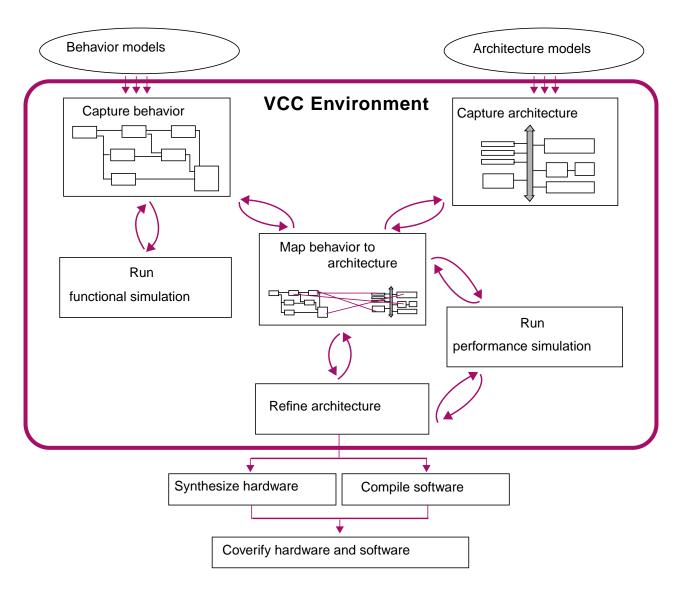

The Cadence® Virtual Component Co-Design (VCC) environment lets you integrate intellectual property models to simulate, evaluate, and select appropriate virtual components for digital communication, automotive, and multimedia system design.

The VCC environment differentiates between a behavior model, which determines *what* the system is supposed to do, and an architecture model, which determines *how* the system is supposed to perform.

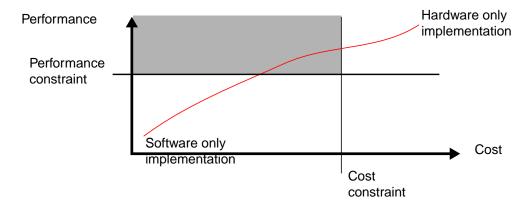

Using the VCC environment, you can explore independent dimensions of behavior and architecture to reach optimal design performance within your given constraints, as shown in the following figure. The gray area of the graph represents the area where performance and cost constraints are met.

Virtual component model developers or vendors can use the VCC environment to accomplish the following objectives:

- To provide models of single-chip or chip-set systems for evaluation and selection by prospective customers

- To integrate virtual component models as building blocks into higher level models

Similarly, system designers and architects can use the VCC environment to accomplish related objectives:

Overview

- To evaluate performance and select models that meet product requirements

- To integrate internally developed or purchased models of hardware and software blocks from Signal Processing WorkSystem (SPW) and other design tools

- To verify that a given behavior can be performed on an existing architecture and still meet performance requirements

- To explore the feasibility of new behaviors on various architectures

# **Integration-Based Design Flow**

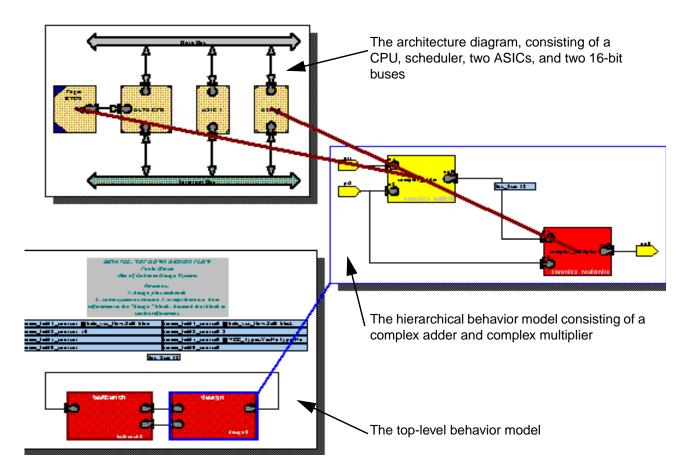

The VCC design flow is illustrated in the following figure.

To begin the process, you capture the desired behavior and verify that the system works through functional simulation. Separately, you capture a potential system architecture using performance models of hardware and software components.

Next, you map the verified behavior diagram to the system architecture diagram. From this mapping diagram, you run a performance simulation to evaluate the performance of the behaviors on the selected architecture. You refine, remap, and reverify until your design meets your performance requirements.

Overview

If a desired architecture is too expensive to implement, you can adjust constraints or functionality to accomplish your goal or declare the behavior unimplementable under the current performance constraints.

### **Capturing Behavior**

Behavior models represent functional system blocks and testbenches. When capturing the behavior of a system design, you specify behavior as high-level behavior models without implying an eventual architecture implementation.

In the VCC environment, a behavior primitive is mapped to a single architecture primitive. It cannot be partitioned across several architecture models. If you want to explore mapping parts of a behavior on separate architecture models, you should compose it as a hierarchy of models. This approach lets you map all the segments on to one architecture model or individual segments on to separate architecture models.

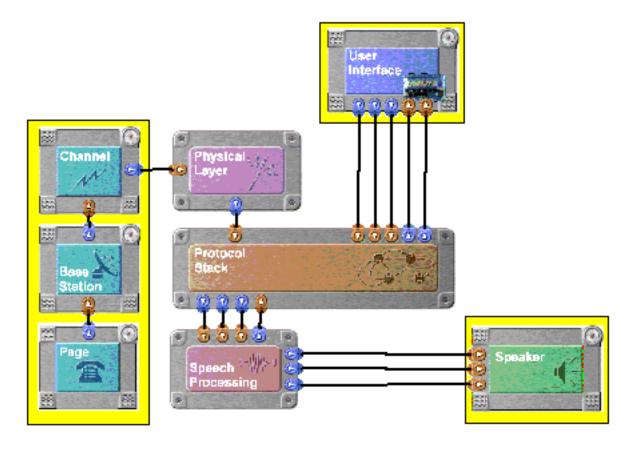

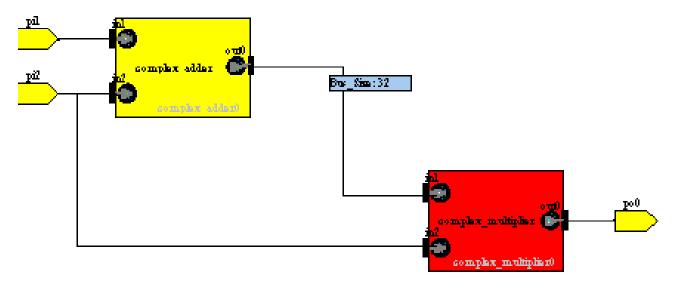

You use the Behavior Diagram Editor to create your behavior diagram. For a new behavior diagram, you instantiate symbols that represent behavior models and set model properties to define model and port characteristics. You connect the input and output ports of the behavioral models to create a system diagram, as shown in the following figure.

Overview

### **Behavior Modeling Tools**

You can use various tools to create libraries of behavior models depending on the role of the models in your diagram.

To import new or existing models, you can use the following tools:

- Use SPW to specify DSP-oriented applications and other synchronous data flow models.

- Use the Telelogic SDT tool to specify graphical SDL models of behavior. This tool is a standard in the telecommunications industry.

To create models in VCC, you can use the following tools:

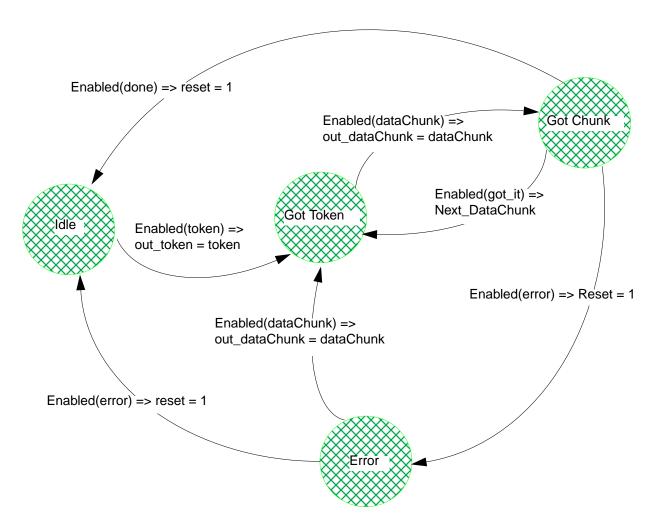

- Use the STD Editor to specify graphically communication refinement and similar codesign finite state machine (CFSM) models.

- Use the text editor in the VCC environment to specify textual SDL models for communication refinements and for CFSM models.

- Use a C software development tool or a text editor in the VCC environment to specify Whitebox C models for embedded software.

- Use a C++ software development tool or a text editor in the VCC environment to specify C++ models for modeling general functional blocks.

# **Running a Functional Simulation**

You should verify the integrity of your behavior design through functional simulation before evaluating the performance of the system. Turnaround time in functional simulation is shorter than in a performance simulation because execution of the blocks is instantaneous. Functional simulation, therefore, is preferable for integrating and debugging behavior models.

In functional simulation, you

- Create an analysis session for your behavior diagram.

- Set design parameters and sweep parameters.

- Place probes and display objects in your design so you can check results.

Overview

Use the Visualize tool to postprocess simulation results.

Linking models into simulator ...

Done.

Overview

# **Capturing Architecture**

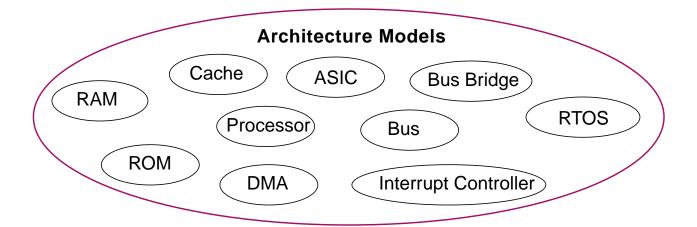

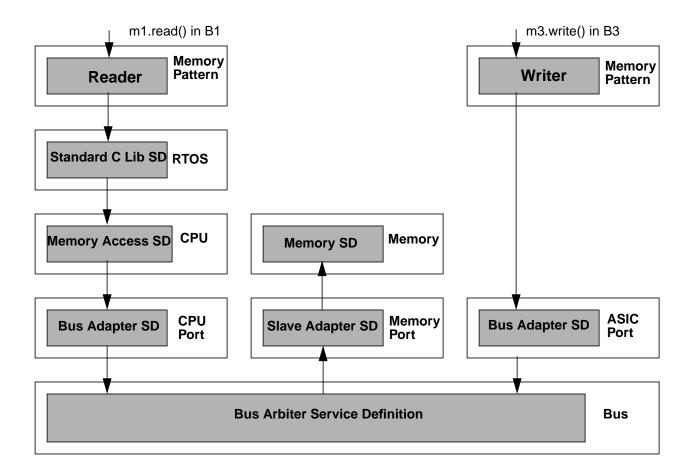

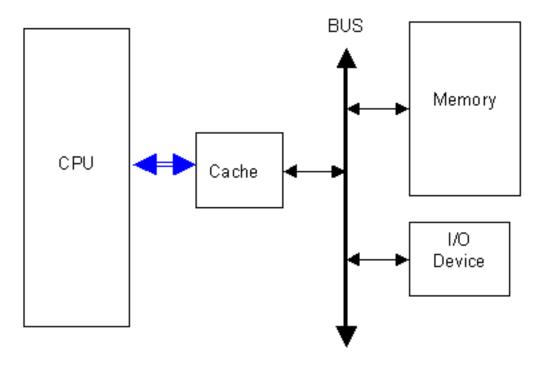

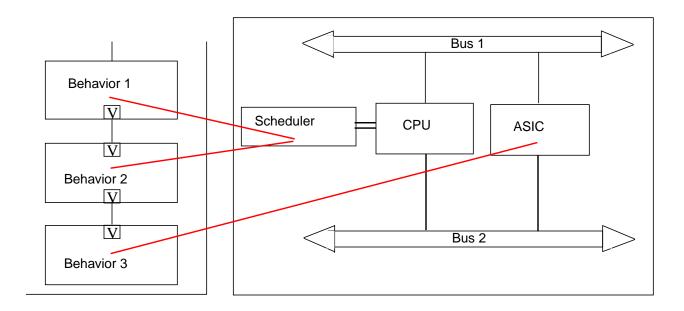

In the VCC environment, potential architectures consist of the models shown in the following figure.

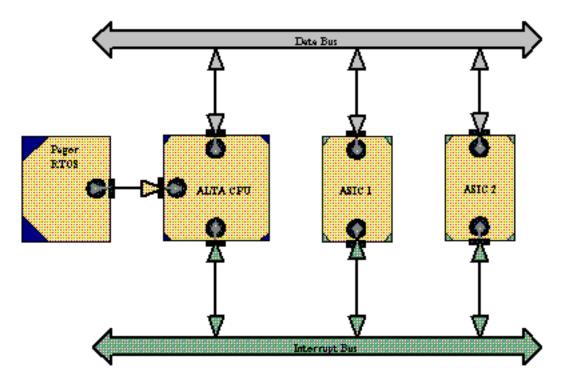

Initially, to capture your architecture diagram, you use the Architecture Diagram Editor. This tool lets you quickly enter a relaxed architecture that represents a target implementation architecture. In a relaxed architecture diagram, you do not need to define every port and signal—you need only define the basic topology.

In an architecture diagram, you instantiate symbols representing various architecture models, such as a bus, RTOS, and processor. You add ports and connect the models to appropriate

Overview

buses, as shown in the following figure. Architecture properties define performance and implementation characteristics.

A performance model must be specified for each architecture primitive model. For example, a processor is characterized by delays of executing instructions.

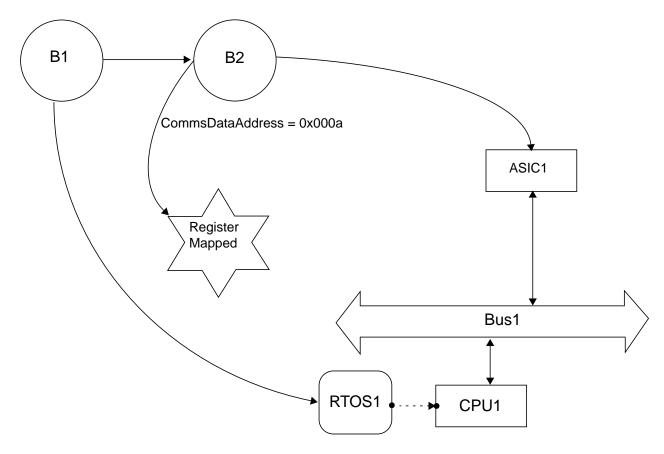

# **Mapping Behavior to Architecture**

Mapping makes the connection between behavior models in a behavior diagram and architecture models in an architecture diagram.

Overview

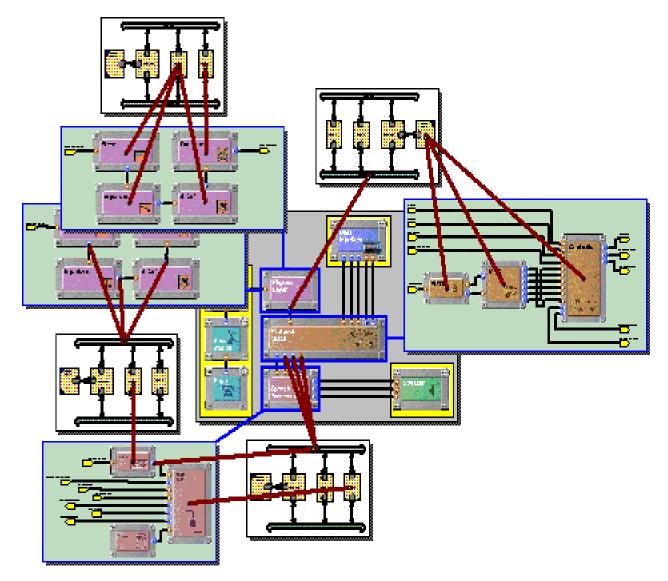

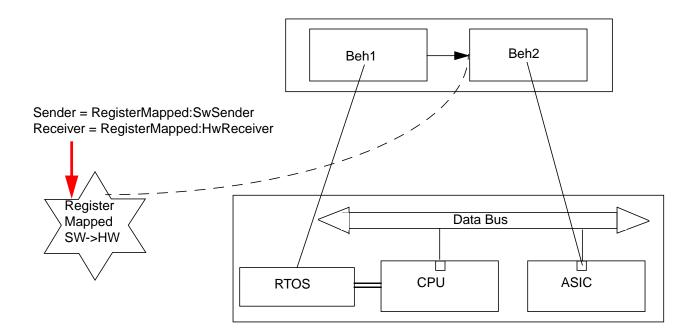

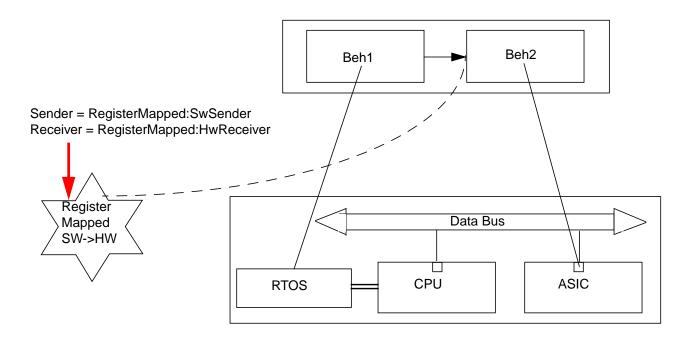

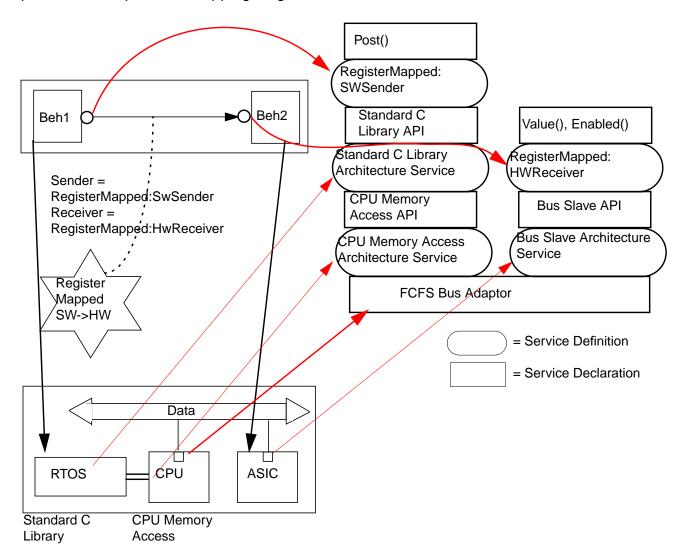

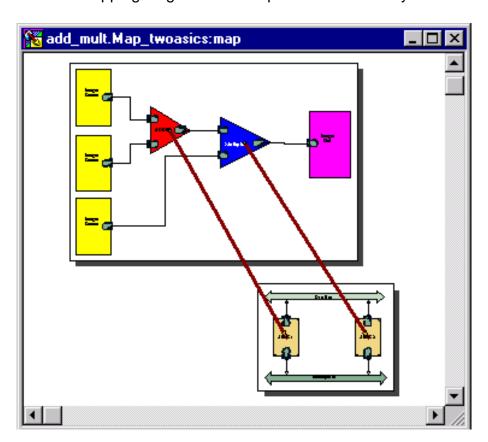

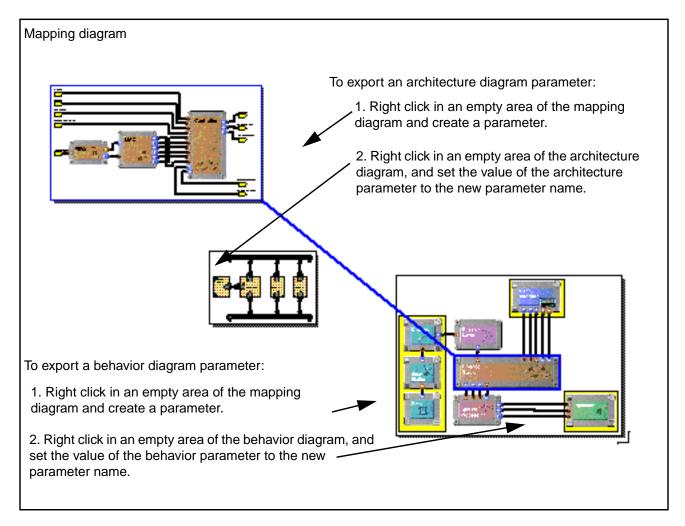

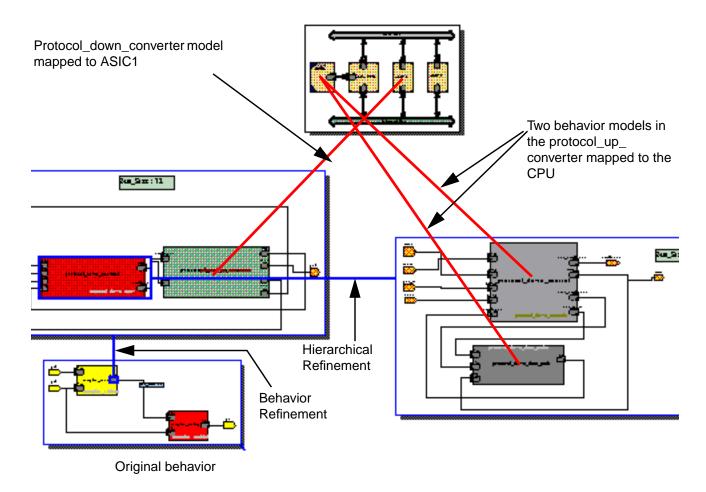

The Mapping Diagram Editor lets you map the behavior to the relaxed architecture, as shown in the following figure.

Mapping defines the hardware and software partitions. For example, behaviors mapped to a scheduler associated with a processor are implemented in software.

Mapping also identifies a performance model that provides the basis for assessing realistic delays incurred if the behavior is run on the mapped architecture.

Architecture models represent performance models that can be used to analyze an implementation of a behavior. Performance models can be precharacterized from an actual implementation or can be user-defined to characterize expected performance based on projected budgets or constraints.

Overview

# **Running a Performance Simulation**

The performance simulator evaluates the performance of the mapped diagram. Performance simulation can

- Identify missed events

- Estimate system-level performance

- Provide data on the usage of processors, buses, and other shared devices

By inserting probes in your mapping diagram, you can collect and graphically display data to assess and compare system function.

Overview

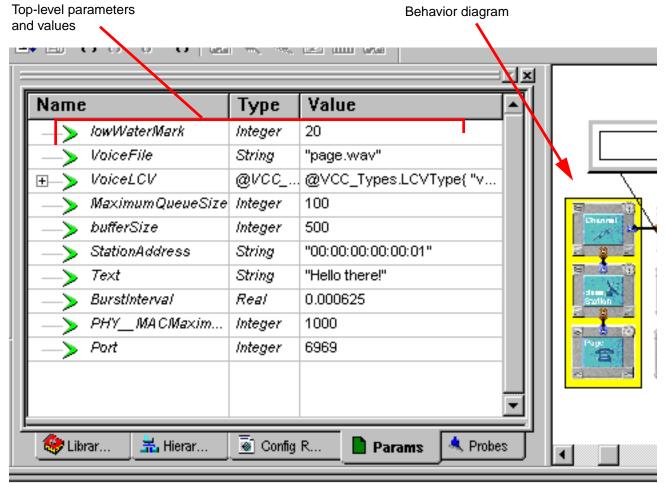

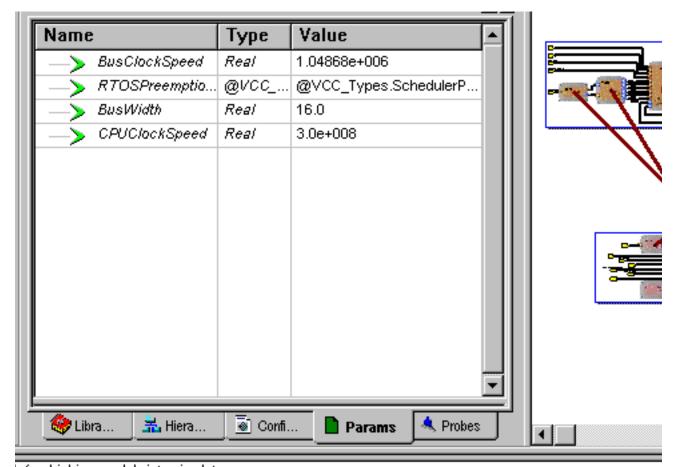

The following figure shows the performance parameters and their settings for a simulation run.

Info: Linking models into simulator ...

Info: Done.

You can remap behaviors to different architecture models, then rerun the simulation to analyze the effects on performance. You can sweep simulation parameter values to compare the performance using different characteristics.

# **Refining Mapping Diagrams**

You can refine your mapped diagram to include more design decisions by

Analyzing behavior delay

Overview

- Analyzing bus traffic

- Refining communication patterns

- Analyzing memory access

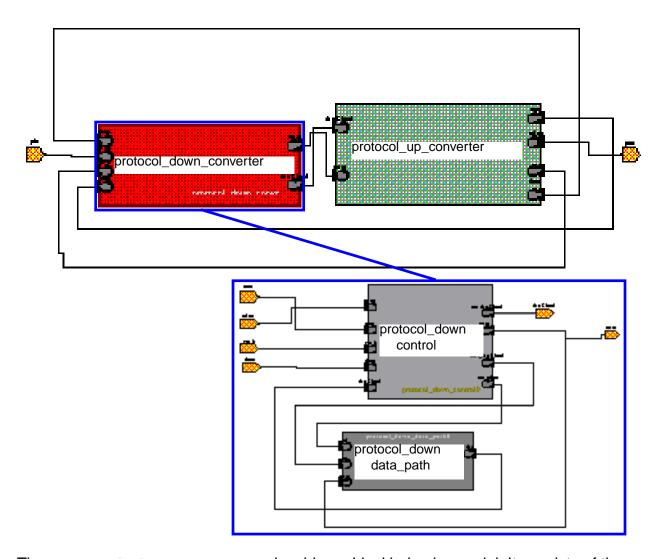

In addition, behavior refinements can include refining communication, specifying refined control protocols, or changing abstract data types to base data types that more closely represent the actual implementation.

# **Exploration**

You can use the VCC environment to explore various possibilities for new product or feature design. The following sections offer several ways to use the features of the VCC environment depending on the goals of your exploration.

### **Derivative Design**

In the VCC environment, you can explore the effects of adding new functionality to existing products.

- Create behavior models for additional features to enhance your original product design.

- Using the mapped diagram from your original product, create multiple mapping diagrams that combine some or all of the new features.

- Simulate and analyze the results.

- Experiment with remapping and resimulating, adding and dropping new behavior models, to obtain combinations that maintain the performance of the original product.

# **Hardware/Software Partitioning Changes**

To explore cost-effectiveness and high performance, you can evaluate the benefits and drawbacks of partitioning various behavior models in hardware or software.

- Use the Save As option to save your current mapping diagram.

- Change the mapping of various behavior models to assess the benefits or drawbacks in implementing certain behaviors in hardware versus software.

- Sweep parameters in all mapping diagrams to compare statistics about each method.

Overview

### "What If" Scenario

The VCC environment can be used effectively to explore potential architecture design combinations. In this type of exploration, you create architecture models and vary performance property values until a design meets your budget or constraint requirements. Once you have determined a suitable architecture, you can search vendor libraries to find virtual component models that meet your model specifications.

- Create and debug a mapping diagram that instantiates your behavior diagram and an architecture diagram that seems appropriate for your needs.

- Export architecture model performance properties that affect your budget or constraints.

- Simulate, analyze, and debug results of the first design's performance.

- Use the Save As option to adjust your initial architecture diagram, using a naming convention that emphasizes the differences in your diagrams. Create, debug, and simulate a mapping diagram for each modified architecture.

- Adjust simulation parameter values and resimulate.

- Sweep parameters in several of your mapping diagrams to analyze multiple options.

- Use Visualize to display multiple windows for statistics and Gantt chart comparisons.

Overview

2

# **Performance Models**

Because the performance of a behavior model is dependent on the architecture, the behavior performance model is described in terms of the services supported by the architecture. For example, the performance model of a behavior model mapped to an RTOS does not know the execution time for the behavior model—the execution time is dependent on the clock speed of the processor and the instruction set supported by the processor. The behavior model only contains the number of instructions to be executed. The architecture service contains the information about the clock speed and instruction set of the processor.

As another example, a behavior model accesses memory for instruction and data fetching. The performance impact of a memory access is dependent on the load of the bus, the transfer rate on the bus, and the memory latency. To model this, VCC supports behavior models that reference services supported by the architecture.

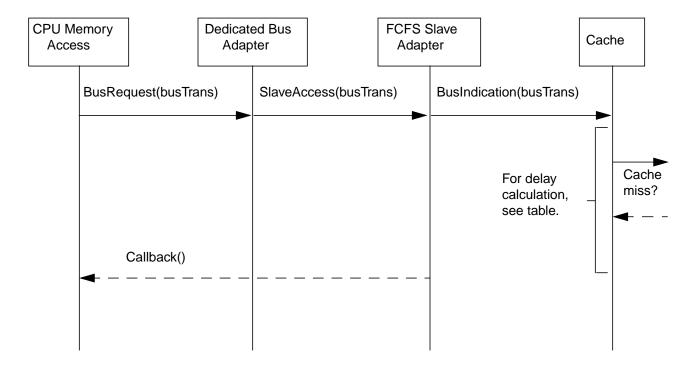

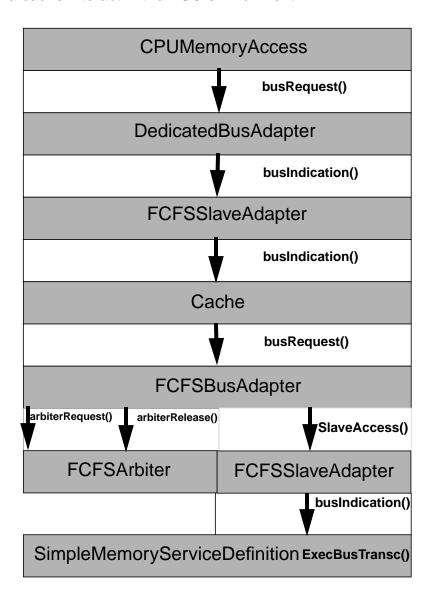

In the first example, the behavior model specifies the number and type of instructions in the behavior model, whereas the performance model of the processor models the cost of an instruction. In the second example, the performance model of the behavior specifies the type of memory access (read/write) and the data size of the request. The performance model of the processor converts the single read/write request into the appropriate number of bus requests, the bus adapter requests ownership of the bus, and the bus model accounts for the performance impact of arbitration. Finally, the appropriate RAM or ROM accounts for the read/write latency. Thus the performance impact is distributed to each of the architecture elements involved in the memory access.

# **Performance Models of Architecture Components**

The performance model of an architecture component is defined by a set of architecture services. These services can be associated with the component itself or with a port on the component. Each service models the performance of a particular function supported by that architecture component. For example, an RTOS might define the following services:

- Scheduler service for arbitrating multiple tasks running on the same CPU

- Standard C library service for modeling standard C functions like memset, memcpy, and sizeOf

Performance Models

- SWInterrupts service for modeling software interrupts

- SWMutexes service for modeling mutual exclusion

Each of these services supports a number of functions. The implementation of a particular function specifies the performance impact of executing that function. For example, the standard C library service models the performance impact of executing the *memset*, *memcpy*, and *sizeOf* functions on a particular RTOS. These services do not implement the functions, rather, they specify the performance impact of calling these functions. In this example, the *memcpy* function blocks for the amount of time needed to write the data to memory—it does not make a copy of the data.

In VCC, the set of functions supported by a service is modeled as a Blackbox service declaration using a C++ header file. The implementation of these functions is modeled as a blackbox service definition using C++. VCC supplies a set of service declarations in the VCC\_ServiceDeclarations library and a set of matching service definitions in the VCC\_ArchitectureServices library. In the case of the RTOS example, the VCC\_ServiceDeclarations.LibCDeclaration:blk\_serviceDecl declares the memset, memcpy, and sizeOf functions, and the

*VCC\_ArchitectureServices.StandardCLibrary:blk\_service* provides the performance impact of each these functions.

# The following is the *blk\_serviceDecl.h* file from the *VCC\_ServiceDeclarations.LibCDeclaration:blk\_serviceDecl* cellview:

```

#ifndef VCC ServiceDeclarations LibCDeclaration blk serviceDecl blk protoface h

#define VCC_ServiceDeclarations_LibCDeclaration_blk_serviceDecl_blk_protoface_h

#include <sim/ModelSupport.h>

template<class portType>

class simulateDLLExport VCC ServiceDeclarations LibCDeclaration blk serviceDecl:

public serviceDeclaration

protected:

VCC ServiceDeclarations LibCDeclaration blk serviceDecl(const ModuleProto&

a, InstanceInit& b)

: serviceDeclaration(a,b) {};

VCC_ServiceDeclarations_LibCDeclaration_blk_serviceDecl()

: serviceDeclaration() {};

public:

virtual vccAddress* memcpy(vccAddress* s1, const vccAddress* s2, size_t n,

vccInstance*) = 0;

virtual vccAddress* memset(vccAddress* s, int c, size_t n, vccInstance*) = 0;

virtual size_t sizeOf(const typeDefinition& type,vccInstance*) = 0;

virtual size t sizeOf(const typeObject& data,vccInstance*) = 0;

void* preCast() {return this;};

};

#endif

```

Performance Models

# The following is the *blk\_service.cpp* file from the *VCC\_ArchitectureServices.StandardCLibrary:blk\_service* cellview:

```

#include "blk service.h"

#include <sim/ModelSupport.h>

VCC_ServiceDeclarations_MemoryAccessDeclaration_blk_serviceDecl<typeObject>::

readWrite rwWrite =

VCC_ServiceDeclarations_MemoryAccessDeclaration_blk_serviceDecl<typeObject>::

static const

VCC ServiceDeclarations MemoryAccessDeclaration blk serviceDecl<typeObject>::

readWrite rwRead =

VCC_ServiceDeclarations_MemoryAccessDeclaration_blk_serviceDecl<typeObject>::

CPP MODEL IMPLEMENTATION::CPP MODEL IMPLEMENTATION(const ModuleProto &proto,

InstanceInit &inst)

: CPP_MODEL_INTERFACE(proto, inst), initialized_(false)

void CPP MODEL IMPLEMENTATION:: Initialize(const char* name, vccInstance* block)

void CPP_MODEL_IMPLEMENTATION::Init()

if (initialized )

return;

initialized_ = true;

bytesPerWord_ = typeInfo.getSizeOfWord();

/***********************

Name:

memcpy

Description:

Copies n bytes from memory address s2 to s1. This

implementation assumes that addresses lies on memory

word boundaries. No actual data is designed to be

stored or read. Memory transactions are generated for

performance reasons only.

Always returns s1.

Return:

vccAddress* CPP_MODEL_IMPLEMENTATION::memcpy(vccAddress* to, const vccAddress*

from, size_t n, vccInstance* inst)

MS_DEBUG(2) InfoOut << Start << "memcpy()" << End;

if (n == 0)

return to;

Init();

unsigned reqTrans = n / bytesPerWord_;

reqTrans = ((reqTrans==0) ? 1 : reqTrans);

unsigned remTrans = regTrans;

```

### Performance Models

```

theBegin:

if (remTrans == 0) goto theEnd;

if (from)

memAccess.reference(*from, bytesPerWord_, rwRead,inst,true);

else {

// tbd

if (to)

memAccess.reference(*to, bytesPerWord_, rwWrite,inst,true);

else {

// tbd

}

remTrans--;

goto theBegin;

theEnd:

return to;

/************************

memset

Description: Sets the first n bytes of memory at address s to the value

of c (converted to an unsigned char). Memory transactions

are generated for performance reasons only.

Return:

Always returns s;

*************************************

vccAddress* CPP_MODEL_IMPLEMENTATION::memset(vccAddress* s, int c, size_t n,

vccInstance* inst)

MS_DEBUG(2) InfoOut << Start << "memset()" << End;

if (n == 0)

return s;

Init();

vccAddress* to = s;

unsigned remTrans = n;

theBegin:

if (remTrans == 0) goto theEnd;

memAccess.reference(*to, bytesPerWord , rwWrite,inst,true);

else {

// tdb

}

remTrans--;

goto theBegin;

theEnd:

return s;

```

### Performance Models

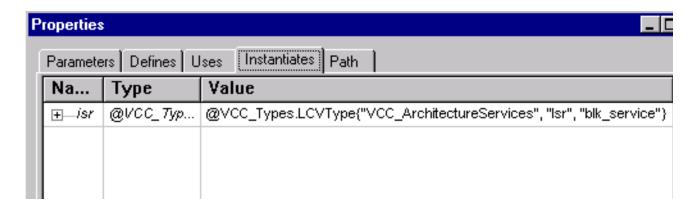

In VCC, the service declarations are associated with the symbol view of the architecture component, and the service definitions for each service declaration are specified in the performance view of an architecture component. For example, a symbol of the RTOS declares that the RTOS supports the

VCC\_ServicesDeclaration.LibCDeclaration:blk\_service. Then, in the performance view of the RTOS, the performance impact of these functions is defined in the VCC\_ArchitectureServices.StandardCLibrary:blk\_service.

The separation of the declaration and the definition makes it easier for you to change the level of accuracy for the performance analysis. You can also choose a different performance type (such as power versus area) by binding a different performance model of the architecture component.

If the performance impact of a service depends on its interaction with another service (either on a different architecture component or its own), the service declares that it uses another service. Specifically it uses another service declaration because it calls a specific C++ function with specific arguments. The service makes a direct call to that function using the *use* handle name, function name, and function arguments.

For example, the *memcpy* function uses the *memoryAccess* service on the CPU to specify the delay for writing the data into memory. The model of the standard C library service calls the *reference* function from the *memAccess* service:

```

memAccess.reference(*from, bytesPerWord_, rwWrite, inst, true);

```

Where memAccess is the handle declared for the memoryAccessDeclaration in the use clause and reference is declared as a function that takes five arguments in the VCC\_ServiceDeclarations.memoryAccessDeclaration:blk\_serviceDecl cellview. In the architecture diagram, the CPU assigned by the RTOS must support the memoryAccessDeclaration for this call to be successful. Distributing the performance models among the architecture components provides the ability to explore different architectures quickly. You can easily change architecture components when the components support the same service declarations.

Performance Models

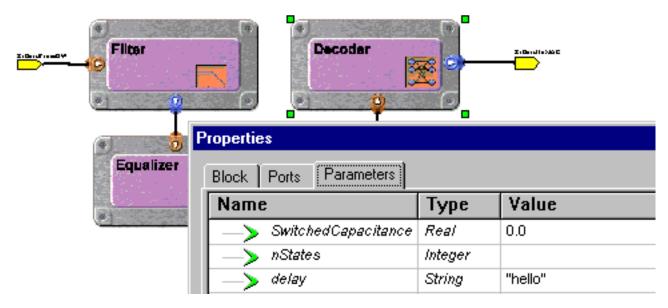

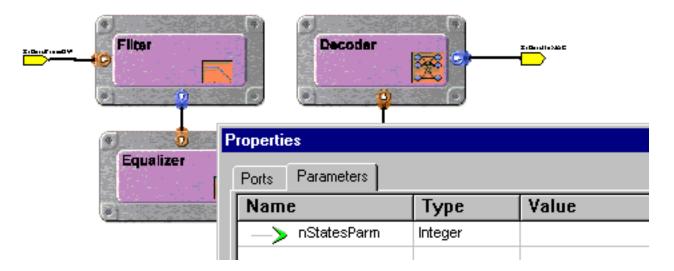

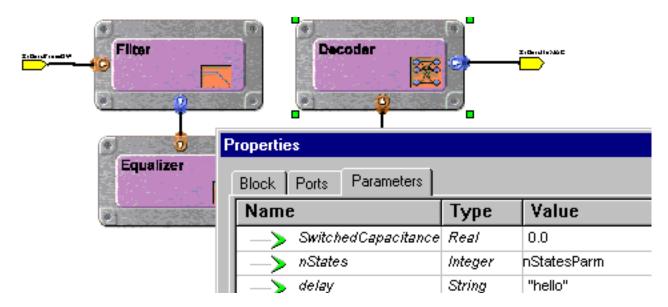

The service definitions can be parameterized. These parameters can be set inside the performance model of the architecture component, or they can be exported to the architecture instance in the architecture diagram. Parameters make the service definition reusable in different architecture components and architecture diagrams.

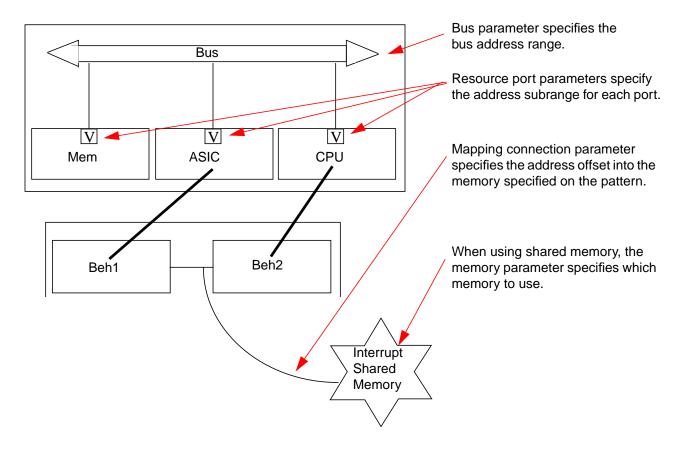

# **Typical Architecture Services**

Service declarations and service definitions can be associated with any architecture resource, and you can also design your own services. The purpose of this section is to provide information about a typical set of services that are applicable to each of the architecture resources.

| Architecture Resource | Applicable Services       |

|-----------------------|---------------------------|

| Processor             | Delays                    |

|                       | CPUInstructionCost        |

|                       | CPUMemoryAccess           |

|                       | CPUInterruptController    |

|                       | CPUSingleStack            |

|                       | CPUTypeSize               |

|                       | FCFSBusAdapter            |

| RTOS                  | SWInterrupts              |

|                       | StandardCLibrary          |

|                       | SWMutexes                 |

|                       | RoundRobinScheduler       |

|                       | SWTimers                  |

| ASIC                  | AsynchronousDelays        |

|                       | StaticPriorityHWScheduler |

|                       | FCFSSlaveAdapter          |

|                       | FCFSBusAdapter            |

|                       | InterruptBusAdapter       |

|                       | Memory                    |

|                       | ASICTypeSize              |

|                       |                           |

Performance Models

| Architecture Resource | Applicable Services |

|-----------------------|---------------------|

| Data Bus              | FCFSArbiter         |

| Interrupt Bus         | InterruptBus        |

| Memory                | FCFSSlaveAdapter    |

|                       | Memory              |

### **Processor Models**

A performance model for a processor should account for the cost of executing instructions. This facilitates writing behavior performance models that are specified in terms of instructions. The processor should also model the performance impact of hardware scheduling and interrupt requests. In addition, the processor should model memory requests (including stack management) and interaction with the bus. These services in turn are dependent on services supported by the connected data bus and the interrupt controller.

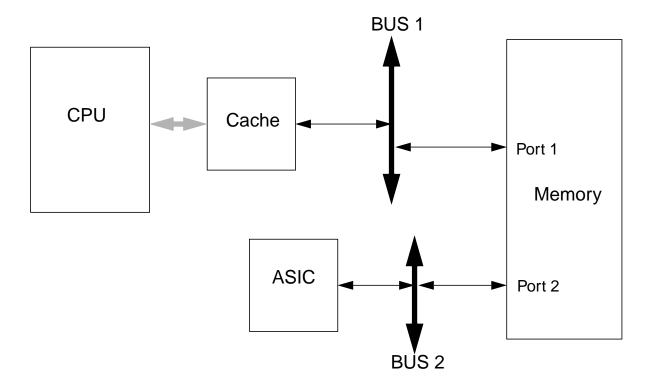

#### **Predefined ASIC Models**

Predefined ASICs are modeled by virtual component providers or library developers by creating an architecture model representing the actual hardware device, one or more behavior models representing the behaviors associated with it, and at least one performance model to support delays, memory access, and bus adapters.

For example, an ASIC provider might supply a library with an MPEG decoder model that consists of an ASIC architecture model, a behavior model providing the algorithm, and one or more performance models.

Using this example, you would instantiate the asic1 symbol in your architecture diagram and choose asic as your performance model. The asic performance model provides services

For scheduling behaviors mapped to it

Performance Models

### For interactions with the databus and interrupt bus

In your behavior diagram, you would instantiate the mpeg\_decoder symbol and make sure blk\_cpp contains the behavior that models the functionality of an MPEG decoder. In your mapping diagram, you would map these two models to each other.

The behavior performance model, delay, describes the performance impact of running the decoder on the asic. You do not need to choose the behavior performance view because the performance model is preset by the BehaviorPerfViewName property in the ASIC model properties.

Refer to your vendor library documentation to determine any link parameter values required by the device.

### **Custom ASIC Models**

A custom ASIC acts as a placeholder for a hardware model that is in development. You need to create an architecture model for the ASIC, one or more behavior models that model the ASIC function, and performance models that characterize its expected performance based on projected budgets or constraints. Refer to the <a href="VCC Modeling Guide">VCC Modeling Guide</a> for details about creating a custom ASIC and a DSL performance model.

You are prompted for exported parameters for every performance model. You need to set only those parameters that are used in the configuration you have selected.

A scheduler model must be included internally as part of the model. If the ASIC includes a scheduler that is parameterized, you might need to assign link parameters.

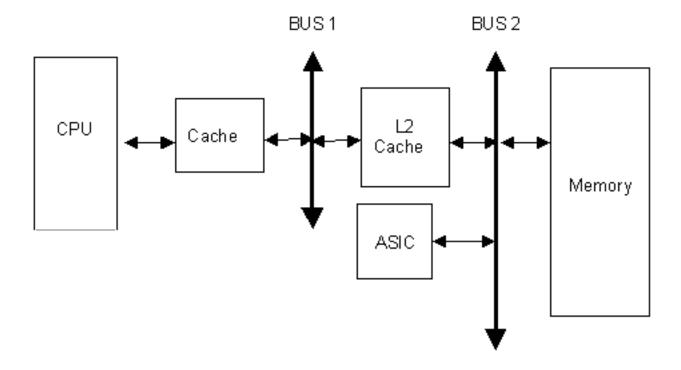

### **Data Bus**

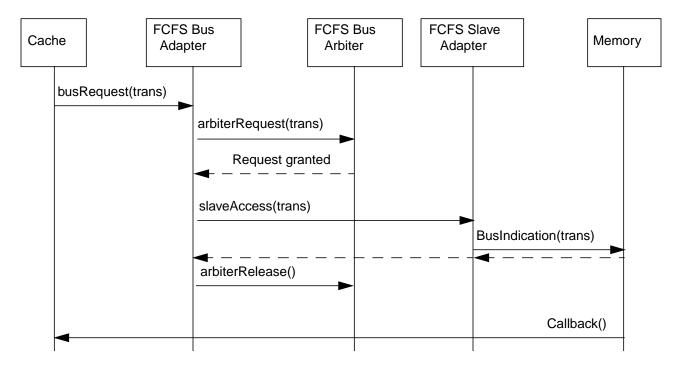

The performance model for a data bus should model the arbitration for bus ownership. Examples of different bus arbiters are first-come-first served, time-sliced, and broadcast. The arbitration of the bus is typically requested by the bus adapter service on the bus master (such as the processor).

Once the adapter has ownership of the bus, the adapter starts transferring the data to the slave adapter (such as to the memory or ASIC). If the bus transaction is addressed to a particular slave, the appropriate slave adapter must first be identified by looking up the

Performance Models

symbolic address in the bus registry. Therefore, each slave adapter must register itself with the bus registry.

### **Interrupt Bus**

The performance model for an interrupt bus should model the contention caused by multiple simultaneous interrupt requests. The interrupt bus should decide the winner and send the request to the interrupt handler (on the processor).

The processor supports an interrupt controller service, which manages the interrupt service routines (ISRs). The ISRs are registered with the interrupt controller. When the interrupt controller gets an interrupt request, the appropriate ISR is scheduled based on the interrupt priority and the currently running task.

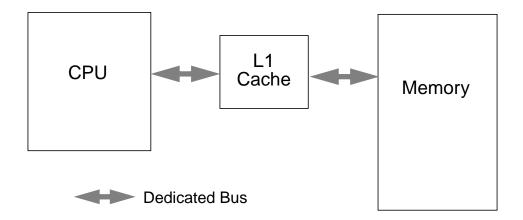

### Memory

The performance model of a memory should model the read/write latency. A *slaveAdapter* service on the port models the interaction with the bus. The memory typically does not manage the actual data being read/written— it only models the performance impact of completing the read or write.

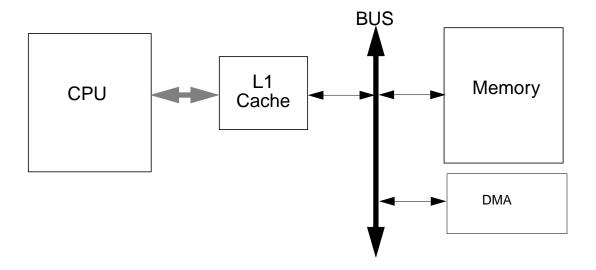

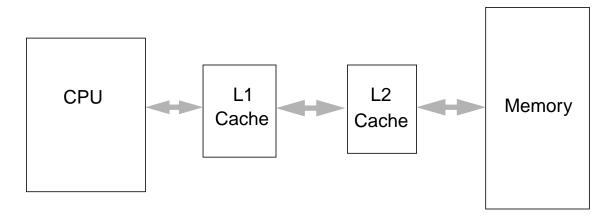

The memory can also be supported by a cache or DMA on the architecture diagram.

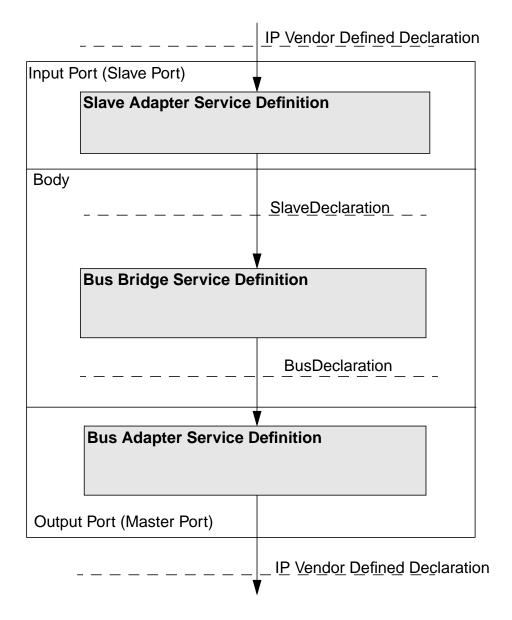

### **Bus Bridge**

The performance model of a bus bridge should model the transfer of data from one bus to another. The bridge typically has a slave adapter on the primary bus and a *busAdapter* (master) on the external bus. When a communication is requested from one architecture component to another, VCC automatically determines the set of buses and bridges needed to complete the path through the architecture diagram.

Performance Models

Because bus bridges can support multiple buses, the legal paths through the bridge must be specified by setting the *vccOutputPortName* parameter on the port.

# **Additional Architecture Services**

Each architecture component in the architecture diagram supports a set of services. Additional services might be appropriate based on the communication paths between these architecture components. For example, a device driver might be useful for the software to communicate with a particular ASIC. However, that device driver is dependent on the processor and possibly the RTOS used in the architecture.

VCC lets you add services to an RTOS in the architecture diagram. These services are defined by a handle name, a reference to a service definition (cellview name), and parameter values required by the service definition. This service definition can use services provided by the RTOS or the processor.

# **Behavior Performance on Software Architectures**

In order to analyze the performance of your system on a specific architecture, you need to specify performance models for each behavior. These performance models can be port delays with parameterization for data type sizes. This approach might be sufficient for hardware, but for software, the performance model is also affected by the following:

- Execution Delays

- Delays Based on the Processor

- Delays Based on Memory Accesses

- Performance Modeling Styles

- Scheduling Shared Resources

# **Execution Delays**

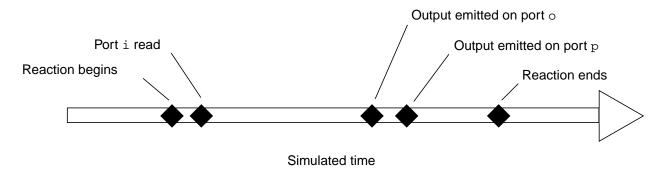

A functional model executes with discrete event semantics. An execution is called a reaction. The reaction samples inputs, computes responses, and emits outputs, all in the same instant.

To make a functional model useful for performance simulation, it must be associated with a temporal model that specifies the execution delays of the reaction. In the VCC environment, you associate a performance model with the functional model.

Performance Models

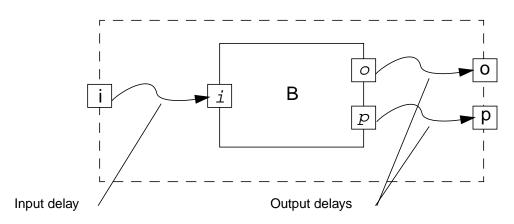

To model the performance of a behavior on some target architecture, you need to specify the instants at which values on input ports are read, the instants at which values on output ports are posted, and the instant at which the reaction ends.

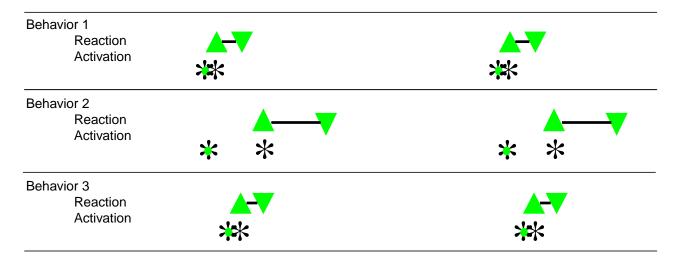

The performance model can be represented as a wrapper around the block, as shown in the following figure.

The performance model causes the reaction to take time. If new values arrive on the input ports faster than the reaction time of the model, events could be lost or missed.

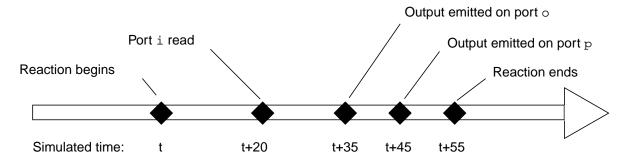

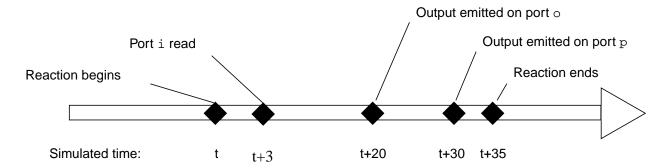

The following figure provides an example of a performance model timeline.

A performance model represents the temporal model of a reaction. The VCC environment defines three types of performance models: annotated C performance models, annotated C++ performance models, and delay scripting language (DSL) performance models.

# **Delays Based on the Processor**

The performance of a behavior running on software is affected by the clock speed of the processor. It is advantageous to parameterize the performance model based on the clock speed of the processor in the mapped design. You can accomplish this in the VCC

Performance Models

environment by referencing the CPS parameter on the processor from within your performance model. (For information about the CPS parameter, see the "Architecture Models" chapter of the <u>VCC Modeling Guide</u>.)

Similarly, the performance of a behavior running on software is affected by the instruction set supported by the processor. For example, a branch or load instruction on a particular processor might require cycle counts different from those of another processor. In order to explore different instruction sets, it is useful to parameterize the performance model based on the processor chosen in the mapped design. You can accomplish this by referencing the processor basis associated with the processor. (For information about the processor basis, see the "Architecture Models" chapter of the <u>VCC Modeling Guide</u>.)

The number of registers on the processor as well as the technique for register allocation also affects the performance of behaviors running on the processor. It is advantageous for the performance model of the behavior to account for usage of registers. In the VCC environment, the annotated C modeling style supports different register allocation techniques for more accurately modeling this impact. (For information about the annotated C modeling style, see the "Architecture Models" chapter of the <u>VCC Modeling Guide</u>.)

# **Delays Based on Memory Accesses**

Execution of a behavior on a processor requires memory accesses for instructions and data that are assigned to specific segments in an architecture memory. The processor must issue a request to access the memory and transfer the memory segment across the bus. In addition, there is a performance impact of accessing data from a processor stack. This can be modeled in the VCC environment by declaring behavior memory segments and mapping them to architecture memories.

In the performance model, the memory segments are declared by name and size. The size specification is of type *String*, which can be parameterized by the size of the instruction. The following example shows a performance model that has two memory segments:

```

segmentName = "data" with size = "1024"

segmentName = "text" with size = "OP.i + LD + OP.i + ST + OP.i + IF"

```

During mapping, these memory segments are collected and presented as a single, uniquely named list of memory segments per processor. These memory segments are used in the linker/loader stage when building the software image.

The complete list of memory segments are gathered from

- Performance views of all behaviors mapped to the RTOS or nested scheduler.

- Services associated with the memory references and timer references of the behaviors mapped to the RTOS or nested schedulers.

Performance Models

- Sender services of patterns associated with the output ports of the behaviors mapped to the RTOS or nested schedulers.

- Receiver services associated with the input ports of the behaviors mapped to the RTOS or nested schedulers.

- Services supported by the RTOS or any nested scheduler.

- *Instantiate* clauses in services. For example, timerTickISR, ISRs for interrupt patterns, and polltaker behavior.

- Software explicitly added to the RTOS using the Add Software command in the Mapping Diagram Editor.

### **Example**

Behavior instance "b1" has the following memory segments:

```

"data" of size "256"

"d1" of size "256"

```

Behavior instance "b2" has the following memory segments:

```

"data" of size "256"

"d2" of size "512"

```

As a result, the processor has the following linker segments:

```

"data" (calculated size of 512)

"d1" (calculated size of 256)

"d2" (calculated size of 512)

```

In this example, the processor linker segment "data" has a calculated size of 512 because the "data" memory segments from instances "b1" and "b2" are combined.

You map each linker segment to an architecture memory by specifying "Memory Participant" and "offset". You also specify the type of the segment, which can be "CODE", "DATA", "STACK", or "HEAP".

The VCC software can automatically calculate the "size" field for each processor segment by adding the sizes of the individual segments of the behaviors mapped to the processor. You can also override this value. The "size" field is represented by a composite type with a field for "size" and a field for "Fixed" or "Floating". If "Fixed," you specify an integer for the size. If "Floating," the VCC software gathers the sizes and uses the *processBasis* file to convert strings to unsigned.

VCC uses the *directMemoryRead* pattern to model the communication of the processor to the specified architecture memory for instruction and data fetches.

Performance Models

# **Performance Modeling Styles**

There are three types of performance models:

- Delay scripting language (DSL) performance models

- Annotated C performance models

- Annotated CPP performance models

### **DSL Performance Model**

The DSL performance model is a method of associating a delay model with a functional model using the delay scripting language (DSL). A DSL performance model can be used in the following situations.

- When the code is not yet fully developed

- When using a blackbox behavior model in which the code is not accessible

- When a processor basis file does not exist

- For hardware

Under certain circumstances, VCC supports backward compatibility for DSL semantics. There is a DSL parameter that causes a DSL script to be interpreted in a way that is compatible with previous releases of VCC. The DSL semantics used prior to VCC 2.0 are still available if you specify the VCC1XMode mode parameter (of type Boolean) on the DSL view of the model and set the value to True. If you use this setting, make sure the pre-VCC 2.0 compatible services are used by the behavior for all port connections.

DSL primitives can sample inputs, perform delays, and post outputs. The delays can be constants, or they can be parameterized by the behavior model, the architecture model to which the behavior is mapped, or the state of a viewport in the behavior model.

The following table describes the semantics of some key DSL primitives.

| input(port)  | Defines the point in the reaction at which the read of the input port occurs.                                                                                                                         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| output(port) | Defines the point in the reaction at which the posting to the output port occurs.                                                                                                                     |

| run()        | This does not have any effect in VCC 2.0, but as in earlier versions of VCC, it is a required separator between the uses of the input primitives and the uses of the output primitives in the script. |

Performance Models

delay(expr) Delays the simulation time from the current instant by the number of seconds specified by the expression.

Other commands are available in the DSL language. For more information, see the <u>VCC</u> <u>Modeling Guide</u>.

The following code segment shows a DSL script that models a behavior implemented on a target architecture.

```

#pragma "DELAY MODEL VERSION" "1.0"

delay_model( )

/* Wait before reading input. */

delay('20e-6');

/* Now read the input. */

input(inA);

run();

/* Wait before posting outputs. */

delay('10e-6');

/* Post the output */

output(outX);

/* Wait between outputs, if needed. */

delay('10e-6');

output(outY);

/* Wait for internal state to finish. */

delay('10e-6');

}

```

This DSL example generates a temporal behavior similar to the timeline in the following figure.

**Note:** The output port statements must be in the same order as the execution of the functional model.

If a viewport is available on a functional model, an internal state variable can be referenced in a delay expression or in the conditional clause of an if statement. See VCC Help for details about using viewports.

The following DSL model is dependent on the input data and the attributes of the behavior model and architecture model.

Performance Models

```

#pragma "DELAY_MODEL_VERSION" "1.0"

attribute integer ntaps;

attribute real cps;

delay_model()

{

//First, read the input value.

input(iblock);

run();

//Now, delay according to how long it takes to do an FIR.

delay('((real) ((5 + iblock.npts) * (5 + ntaps))) / cps');

//For each output port, add ouput statement.

output(oblock);

}

```

In this script, there is an input port named *iblock* of composite type with an integer field called *npts*. The behavior model has an integer property called *ntaps* that is declared as an attribute in this model. The architecture model has a real performance property called *cps* that represents the clockspeed as cycles per second. The *cps* performance property is also declared as an attribute of this model. The casting operator *real* converts the integer expression to a real value because the *delay* expression must evaluate to a real expression.

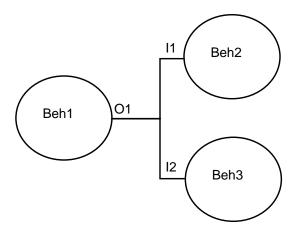

# **Restrictions in DSL Semantics to Support Services**

In previous VCC releases, you could use DSL to control both the order in which the outputs propagate from a block as well as the time delays between these output propagations. With the use of services in the current release, it can be the behavior, not the DSL script, that controls the order in which the outputs propagate from a block. You can use DSL to control the time delays between the output propagations. However, when a non-zero delay separates two output propagations (that is, a use of the 'delay' primitive with a non-zero parameter separates two uses of the 'output' primitive), the output port ordering in the DSL script must be consistent with the ordering from the execution of the behavior.

Furthermore, the behavior may execute, at most, one *Post* operation on a given output port in any reaction. The following example illustrates these points.

#### **Example**

Consider a behavior model with two output ports, o1 and o2, as follows:

The corresponding DSL script is incorrect if it looks like this:

#### Performance Models

# **Annotated C Performance Model**

The annotated C performance model is derived from a clearbox or whitebox model. The original model is annotated with inline delay calls and memory accesses to create the annotated C performance model. The VCC software estimator automatically inserts the annotations. Note that this technique is only applicable when you are mapping your behavior to a processor.

The VCC software estimator reads a restricted form of C code and estimates the cost of execution of each basic block. These estimates are parameterized by the cycle counts specified in the processor basis file. In addition, the software estimator inserts memory accesses for instructions and data fetching and estimates the size of the memory segments. The performance model is also impacted by the register allocation technique chosen for the model.

You can control many features of the software estimator. For more information, see the <u>VCC</u> <u>Modeling Guide</u>.

This performance model generates a temporal behavior similar to the following timeline:

# **Register Allocation**

Without register allocation, VCC assumes that all variables are allocated to memory. The software estimator attributes a delay for loading variables from memory into registers prior to each use of the variable, and for storing variables in memory after each use. Using this method, the delay incurred by memory accesses might be pessimistic.

Performance Models

To improve this estimate, you can use register allocation for variables in a Whitebox C model in order to more closely estimate the actual processing cost of accessing variables. Register allocation assumes that as many registers as necessary are available and will be used. This implies that every use of a given variable does *not* result in a load and that every definition of the variable does *not* result in a store.

You can use register allocation for local scalars, parameters, or both. When you select one of these options, SUB and RET instructions in the processor basis file provide estimates for the cost of saving and restoring registers. Without register allocation, LD and ST instructions estimate the cost of memory load and store operations, which incur larger delays.

Note that register spills are not estimated. If the number of local scalar variables might exceed the number of general purpose registers, such as in data path code, this estimation might be optimistic. For most control path code, however, this estimation should be acceptable.

# Annotated C++ Performance Model

The annotated C++ performance model is specified by inserting performance calls directly into your Blackbox C++ behavior model or service definition. This is the most general modeling style, which lets you model delays caused by the control structure of the model. You also have more freedom to model the performance at different levels of accuracy.

Performance calls in a behavior or service definition are made to routines specified in service declarations. The following four service declarations are useful in annotated C++ performance modeling:

- DelayDeclaration

- MemoryAccessDeclaration

- InstructionCostDeclaration

- ImplemenationSizeDeclaration

The details on the routines available in these services declarations can be found in the <u>VCC</u> <u>Library Reference</u>.

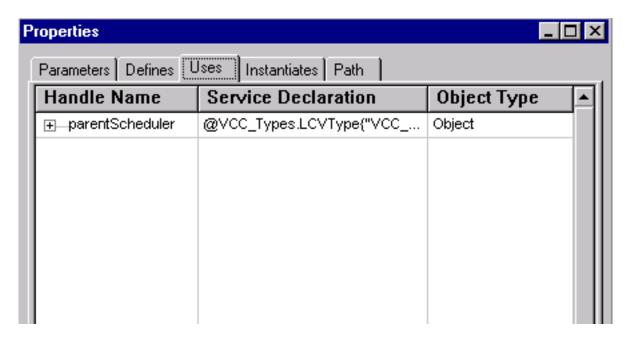

Before one of these service declarations can be used by the model, you must place it in the *Uses* tab, which is available when you are editing the properties of the model. (To access the *Uses* tab, open a .cpp file from Create, right click inside the text editor window, and choose *Properties*.)

In general, performance calls in the C++ model have no effect if the model is used in a functional simulation.

Performance Models

In a performance simulation, you must be able to bind the service declarations used for the performance calls to service definitions based on the mapping to architecture design. For example, the *InstructionCostDeclaration* service declaration is typically supported only by a processor, and if the behavior is mapped to a RTOS running on that processor, the implementation of *InstructionCostDeclaration* associated with that processor will be used. If, on the other hand, the behavior is mapped to an ASIC, it is unlikely that there will be an implementation of *InstructionCostDeclaration* available to satisfy binding.

# **Using DelayDeclaration**

You use this service declaration to specify delays during a performance simulation. Delays can be expressed in terms of clock cycles or absolute time. See the <u>VCC Library Reference</u> for details of this service declaration.

The following example illustrates how you can use the *DelayDeclaration*.

### **Example**

```

void CPP_MODEL_IMPLEMENTATION::Run()

{

...

// Delays this behavior for two clock cycles. Assumes the

// DelayDeclaration "Handle Name" on the "Uses" properties

// tab for the model is "delayInterface".

delayInterface.delayCycle(this, 2.0);

...

}

```

# Using InstructionCostDeclaration

You use this service declaration for delay modeling based on a set of architecture-independent virtual instructions. For more details on this service declaration, see the <u>VCC</u> <u>Library Reference</u>, and for more details on these virtual instructions, see the information about annotated C delay models in the "Architecture Models" chapter of the <u>VCC Modeling</u> <u>Guide</u>.

One way in which you can use the *InstructionCostDeclaration* in a C++ model is by combining it with the *DelayDeclaration* to specify delay in terms of a set of virtual instructions. The actual delay will vary depending on the mapping behavior and the costs assigned to those instructions on the target processor.

The following example illustrates how you can use the *InstructionCostDeclaration*.

Performance Models

# **Example**

# **Using MemoryAccessDeclaration**

This service declaration provides routines for modeling memory references. References may be made with respect to particular memory segments of the caller, or with respect to a particular value of the *vccAddress* type. Both reading and writing references are supported and the length of the reference is specified as an integer number of bytes. See the *VCC*<u>Library Reference</u> for details of this service declaration.

If you use memory segments, you should define the memory segments for the behavior or service definition model. Do this in the *Memory Segments* section of the *Parameters* tab when you are editing the properties of the model from a behavior diagram. Also, you should map the memory segments on the corresponding processor on the mapping diagram. Do this on the *Link Memory Segments* command on the processor.

# Annotating Code/Data Memory References in Blackbox C++ Annotated Models

After you have specified the code/data segments as a property of your model, you can annotate your model with memory accesses to these code/data segments.

Typically, in the *init()* function, you get an index to the memory segment address for faster access

```

unsigned module, codeSeg, dataSeg;

void Init(){

...

module = memDeclaration.registerModule(this);

codeSeg = memDeclaration.registerModuleSegment(module, "code");

dataSeg = memDeclaration.registerModuleSegment(module, "data");

}

```

Then, in your Run() (or other service functions), you can write:

Performance Models

```

void Run(){

...

// Read 20 bytes from text segment offset 50

memDeclaration.reference(module, codeSeg, 20, 50, memDeclaration.read)

...

}

```

**Note:** The offset specified for code/data memory reference is written to the segment of this service definition. This segment is then mapped to a specific architecture memory. Thus, the behavioral service definition can be annotated independent of the other software blocks and the linking/relocation information.

# Using ImplementationSizeDeclaration

This service declaration provides routines for extracting architecture-specific information such as the sizes of various data types on the target platform. For more information see the <u>VCC Library Reference</u>.

The following example illustrates how you can use the *ImplementationSizeDeclaration*.

# **Example**

# **Scheduling Shared Resources**

When multiple behaviors are mapped to the same architecture model, these behaviors might share the same resources. For example, if multiple behaviors are mapped to an RTOS, they contend for execution time on the processor. In this example, the RTOS arbitrates between the behaviors by implementing a scheduling policy (such as round robin scheduling, priority-based scheduling, and so forth). In the VCC environment, a scheduling policy is modeled by an architecture service on the RTOS or ASIC architecture model.

Performance Models

# **Performance Impact of Scheduling**

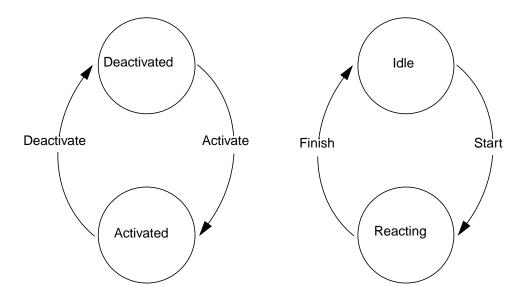

Scheduling involves two fundamental concepts

- Activation—a state of readiness

- Reaction—the run state of a task from the time it starts to the time it finishes.

A task is activated whenever an event is received on any input port. An activated task waits for its assigned scheduler to respond with a start message. Once started, if the task is not suspended, it reacts until its performance model signals that the reaction is complete.

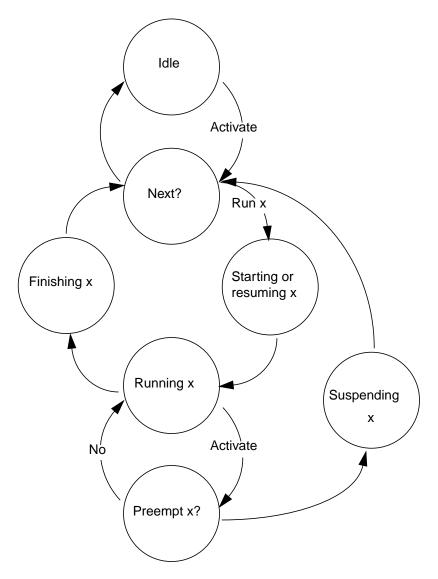

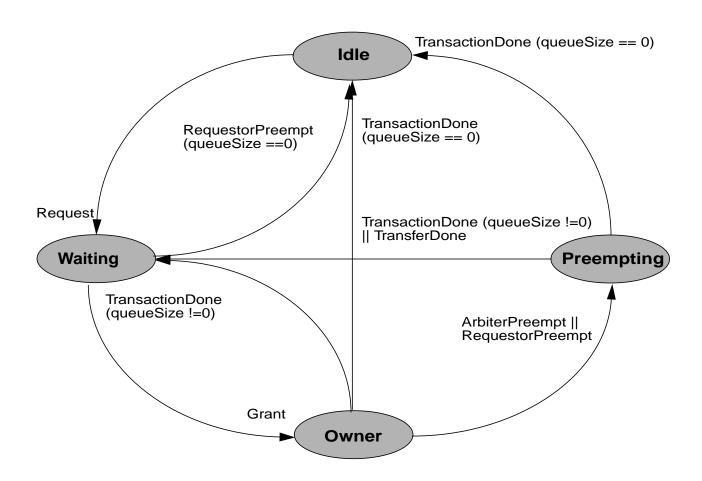

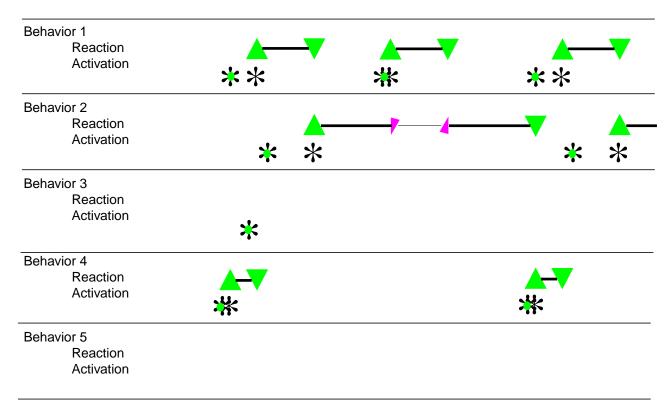

The activity of a task can be represented as a pair of concurrent finite state machines, or the equivalent product machine, as shown in the following figure.

The following transitions signal the conditions for state changes. They are issued by the simulator, scheduler, or a delay model associated with the task, as noted.

| Transition | Sender                                                                                                     | Meaning                                                                                |

|------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Activate   | Sent by the simulator as a result of other behaviors sending input to the behavior represented by the task | The task is ready to run.                                                              |

| Deactivate | Sent to the simulator as a result of receiving a start message from the assigned scheduler                 | The task no longer needs to be activated. (It is already running, or it has no input.) |

Performance Models

| Transition | Sender                                                   | Meaning                   |

|------------|----------------------------------------------------------|---------------------------|

| Start      | Sent by the scheduler to which the task is assigned      | The reaction has started. |

| Finish     | Sent by the delay model that is associated with the task | The reaction has ended.   |

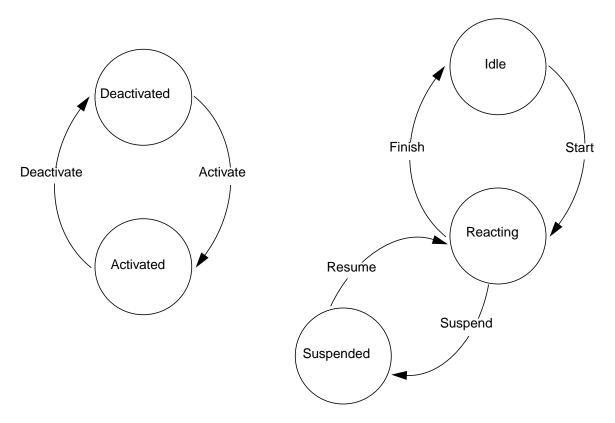

To properly model software, both DSL and annotated C and C++ performance models can be suspended and resumed by an arbitrated scheduler. Suspending a reaction makes time stop for the performance model. Once the reaction is resumed, time begins again. This preemption capability can be fully integrated with the VCC scheduling facility without requiring changes to the functional model.

To support preemption, the scheduler provides an additional scheduler transition:

| Transition | Sender                                              | Meaning                                                              |

|------------|-----------------------------------------------------|----------------------------------------------------------------------|

| Suspend    | Sent by the scheduler to which the task is assigned | Stop processing the current task to activate a higher priority task. |

| Resume     | Sent by the scheduler to which the task is assigned | Continue running the suspended task.                                 |

Performance Models

The following figure illustrates the addition of the suspended state in the task model.

The resume/suspend transition controls changes between the reacting and suspended states.

If preemption occurs after the input sampling phase, it delays the outputs by the duration of the preemption.

If preemption occurs during input sampling, computation might be affected. Input values might be overwritten before they are sampled, or new events might arrive that were not available originally. It is precisely these effects that need to be understood through simulation.

# **Scheduler Services**

In the VCC environment, scheduling is modeled as an architecture service. This service is responsible for managing the state for each of the tasks mapped to it. The scheduler service determines what happens when two tasks request to run at the same time, and it defines the policy for preemption.

Performance Models

Scheduling policies can vary broadly. For example, a scheduler modeling a clock for digital hardware can disregard the notion of activation and start the reactions of all its tasks at a fixed frequency.

In contrast, a scheduler for a real-time operating system (RTOS) tracks activations of tasks as requests for service. In this case, the relation between activation and reaction is a complex function involving activated tasks and a set of priorities associated with them.

Most common scheduling policies are modeled as architecture services in the VCC\_ArchitectureServices Library. The VCC simulator also provides support for modeling single-threaded and parallel-threaded schedulers.

# **Single-Threaded Scheduling Model**

The single-threaded scheduling model transitions a task from one state to another. Receiving an activation notice for one of its assigned tasks triggers one of the following changes.

- If the scheduler is idle, it determines the next task to run based on its scheduling policy.

- If a task is currently running and preemption is allowed, the scheduler determines if the new task preempts the current task. If so, the current task is suspended, and the scheduler determines the next task to run based on its scheduling policy.

If the new task does not preempt the current task, the new task is maintained in the queue until the scheduler determines that it is next.

Performance Models

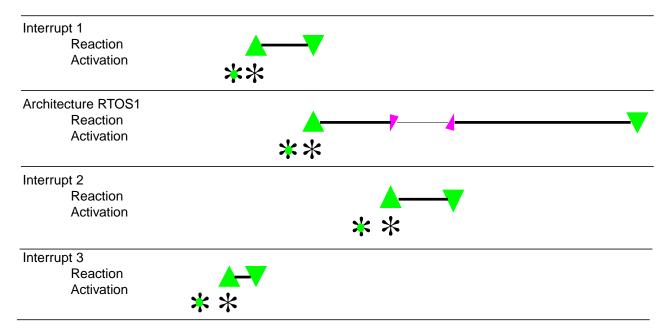

The following figure shows how the scheduler transitions through each state.

Modeling the overhead of scheduling uses delays associated with state transitions for the starting, resuming, finishing, and suspending states of the behavior.

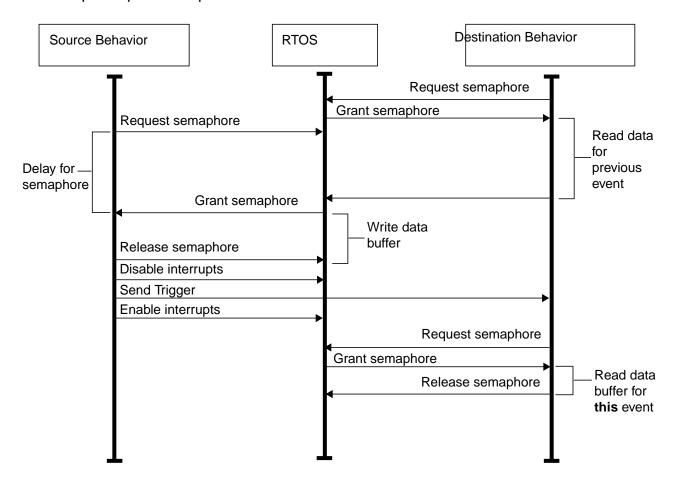

# **RTOS Scheduler Services**

Most application scheduling can use the following standard, single-threaded schedulers supplied in the VCC\_ArchitectureService library.

- Cyclo-static scheduler

- FCFS scheduler

Performance Models

- Static priority scheduler

- Round robin scheduler

To configure these standard schedulers, specify the overheads for transitions in the scheduler states. Refer to VCC Help and the <u>VCC Library Reference</u> for details about setting these overheads when using a scheduler.

# **Cyclo-Static Scheduler**

The cyclo-static scheduler associates an assigned task\_order with each task and executes its assigned tasks on a fixed schedule. The scheduler needs at least one activation request before it can execute. When the scheduler receives an activation, it cycles through its schedule running each task in the order specified, then returns to the idle state. If a block is not runnable when its turn arrives, the scheduler sends an error message and continues with the next task.

Tasks are run from lowest to highest task order.

This type of scheduler is for behaviors that can be statically scheduled, such as a static dataflow.

# First-Come-First-Served (FCFS) Scheduler

The first-come-first-served (FCFS) scheduler runs its tasks in a strict first-come-first-served activation order. When this scheduler receives an activation request, it runs its assigned tasks based on their activation timestamps.

# **Static Priority Scheduler**

The static priority scheduler associates an assigned priority with each task. The priority is fixed for the duration of the simulation. The scheduler runs the task with the highest priority first. By default, the highest priority is defined as the largest task\_priority value of its assigned tasks. This definition can be changed by changing the value of the LargestPriorityIsHigher performance property for this scheduler.

Activated tasks at equal priority are scheduled on a first-come-first-served basis.

This scheduler is parameterized to provide both preemptive or nonpreemptive modes.

Performance Models

#### Round Robin Scheduler

The round robin scheduler associates a static priority with each task. The scheduler runs the task with the highest priority. By default, the highest priority is defined as the largest task\_priority value of its assigned tasks. This definition can be changed by changing the value of the LargestPriorityIsHigher performance property for this scheduler.

Activated tasks at the same priority share the scheduler in a round-robin fashion using a specified time slice. The size of the time slice is configurable by the Quantum performance property.

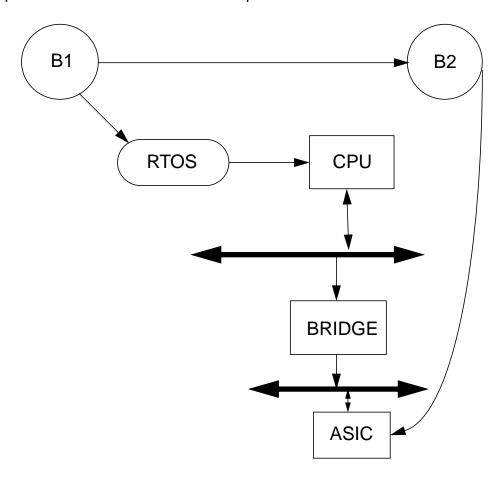

# **RTOS Models**

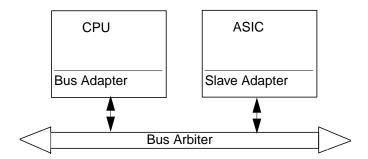

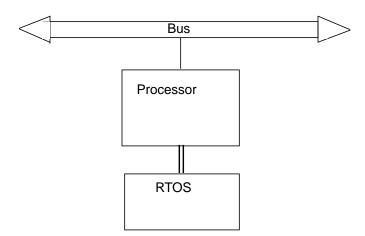

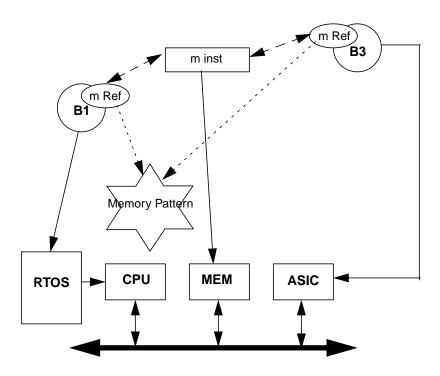

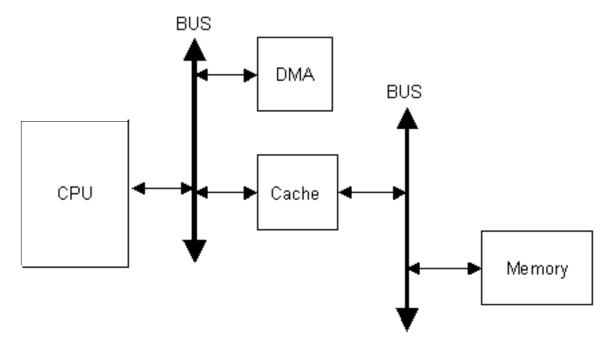

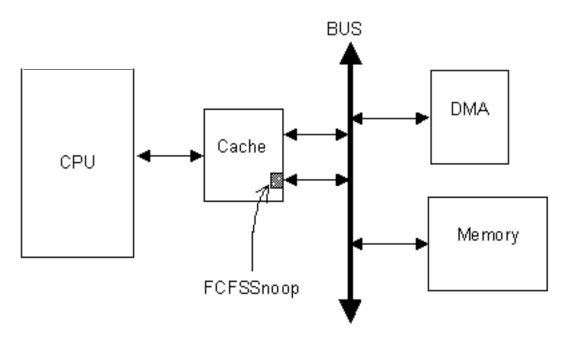

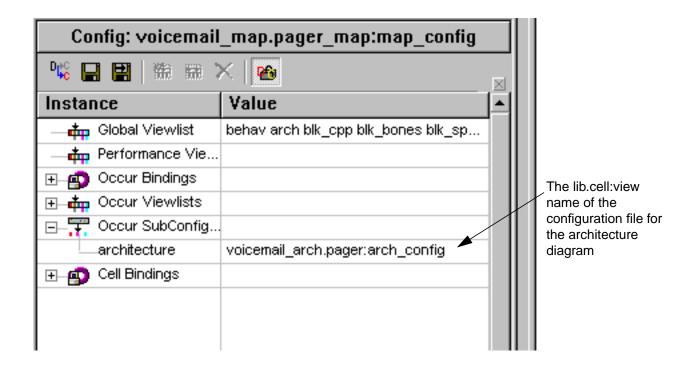

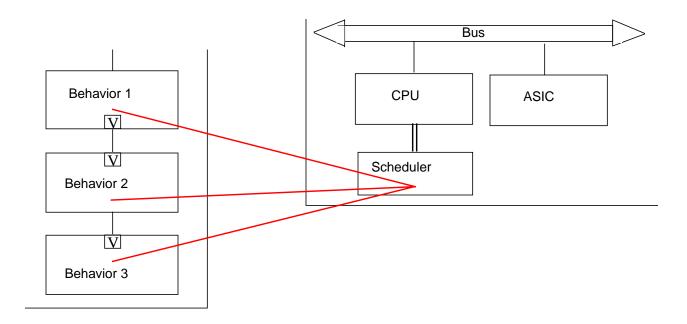

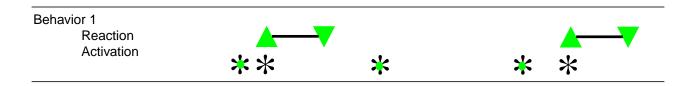

If multiple behaviors are running on the processor model, it requires a scheduler. In the VCC environment, the scheduler for a processor is represented in the architecture diagram as a separate model, as shown in the following figure.

The processor model is attached directly to the bus model. The scheduler model is assigned to the processor model using the *Architecture > Scheduler Assignment* command. (The previous figure shows this connection with a double line.)

Performance Models

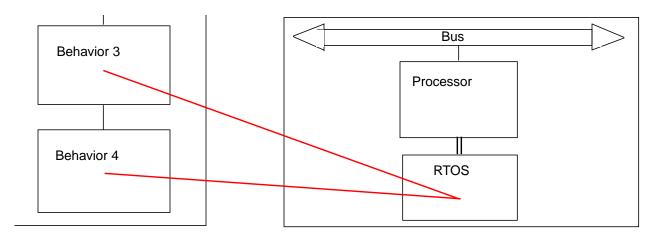

All behavior models accessing the processor are mapped to the scheduler model, as shown in the following figure.

The scheduler model can represent an RTOS or a single task. Both of these representations support a scheduler service to arbitrate the tasks. The RTOS typically provides additional services for standard C library calls, virtual timers, mutexes, and so forth.

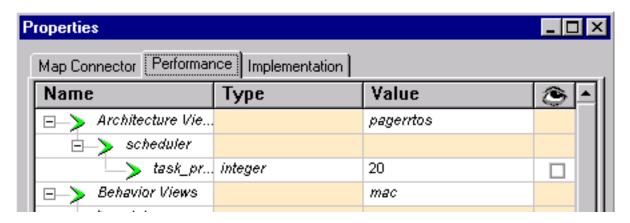

Depending on the scheduler you select, you might need to specify one of the following link parameters (on the mapping link) to sequence tasks.

| task_priority | Priority of the task associated with a specific mapping |

|---------------|---------------------------------------------------------|

|               | connection. Depending on how the scheduler model is     |

|               | defined, a higher value can mean either a high or low   |

|               | priority.                                               |

task\_order Order to execute a task on CycloStaticScheduler.

**Note:** On the mapping link, you are prompted for all link parameters of all performance views of the scheduler. You need only set those parameters that are used in the configuration you have selected.

Refer to Exporting Parameters on page 123 for information about exported parameters.

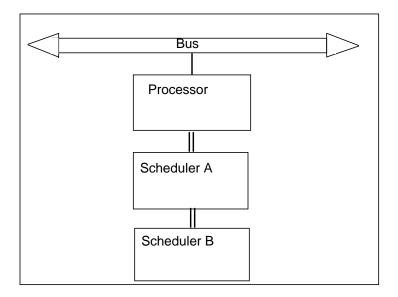

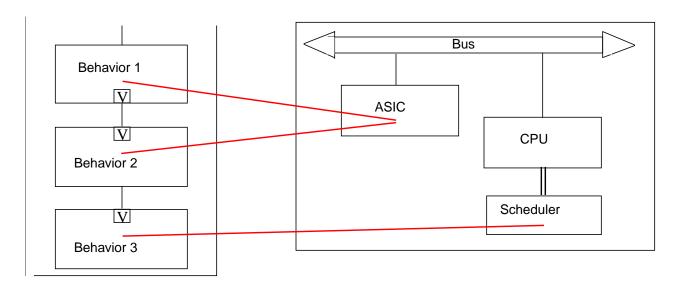

# **Nested Schedulers**

VCC also supports nested schedulers to model more complicated software architectures such as the grouping of multiple behaviors onto a single task that runs its behaviors

Performance Models

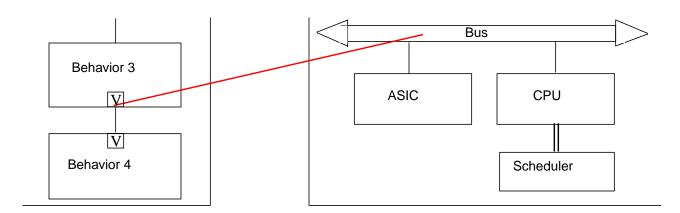

sequentially. The single task is modeled as a secondary scheduler and is assigned to the primary scheduler using the *Architecture > Scheduler Assignment* command.

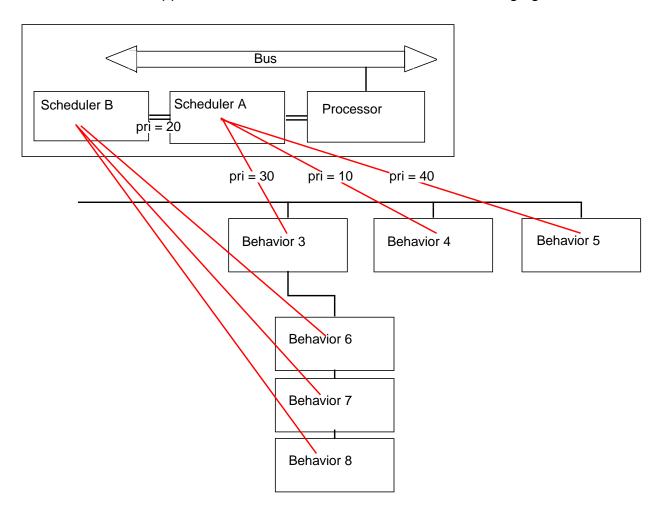

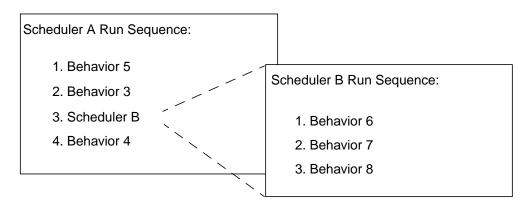

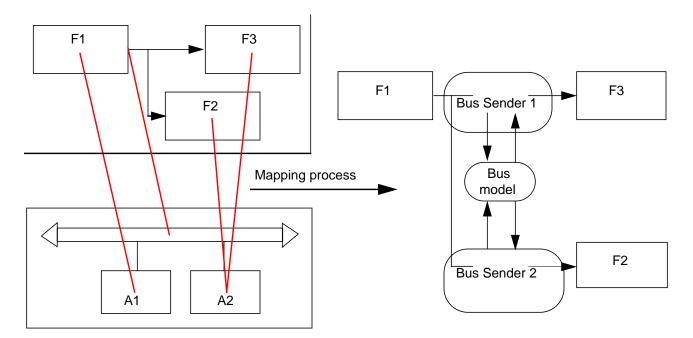

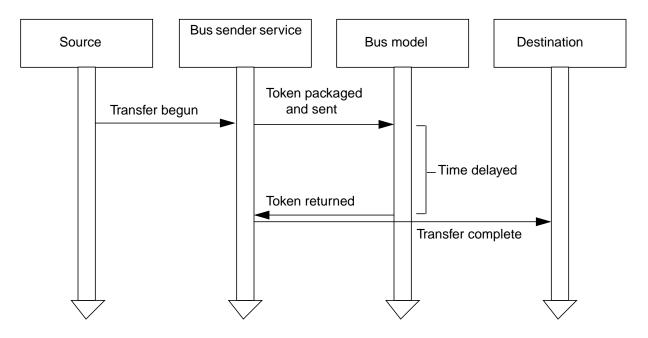

In this illustration, scheduler A is assigned directly to the processor. Scheduler B represents a second tier of scheduling and is assigned to scheduler A, not to the processor.

Scheduler B is considered a task assigned to scheduler A. If scheduler A requires link parameters, these parameters need to be set for the assignment between schedulers A and B. For example, if scheduler A has a prioritized scheduling policy, a task\_priority link parameter needs to be set for scheduler B.

Performance Models

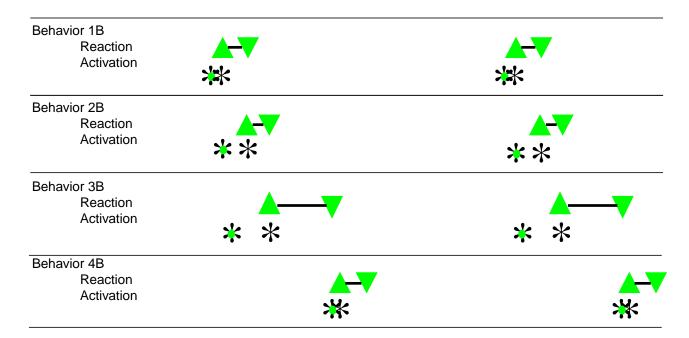

Behaviors can be mapped to both schedulers, as shown in the following figure.

Each mapping represents a task assigned to one of the schedulers. In this example, the mapped behavior models 3, 4, and 5, as well as scheduler B, are assigned to scheduler A. Behavior models 6, 7, and 8 are assigned to scheduler B.

How each behavior is mapped to a scheduler affects the run sequence of the behavior. Scheduler A handles all tasks assigned to it based on its scheduling policy. Scheduler B sequences its assigned tasks based on its own scheduling policy. When scheduler B is ready to run, all behaviors assigned to it are processed as a task flow on scheduler A, but in the sequence determined by the policy of scheduler B.

For example, a static priority scheduling policy can be used to sequence the tasks on scheduler A, while a first-come-first-served scheduling policy can be used to sequence the

Performance Models

tasks on scheduler B. The following illustration provides a possible sequence of events for this example.

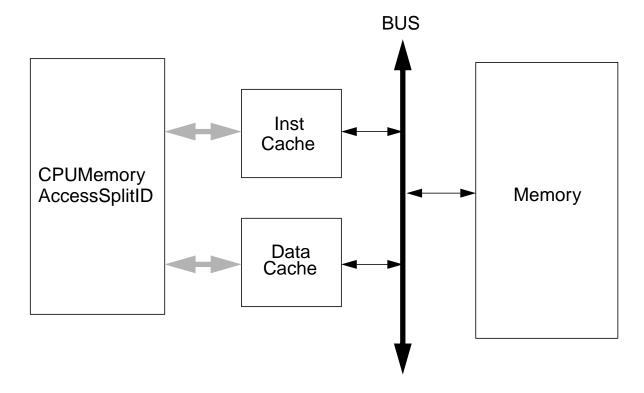

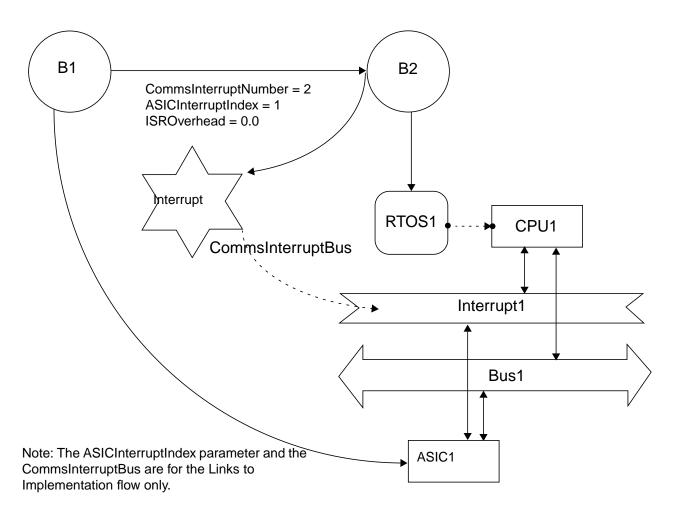

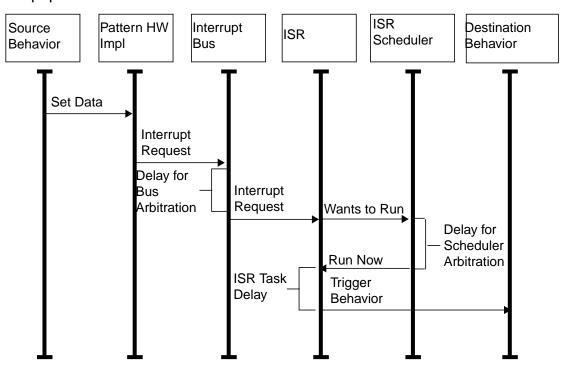

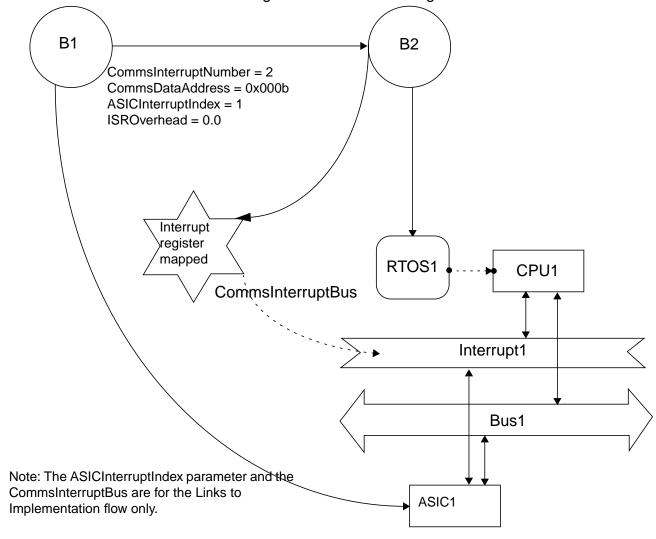

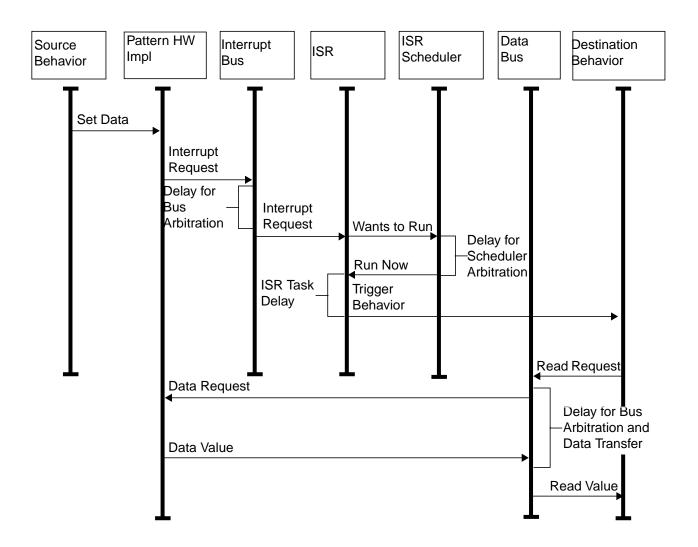

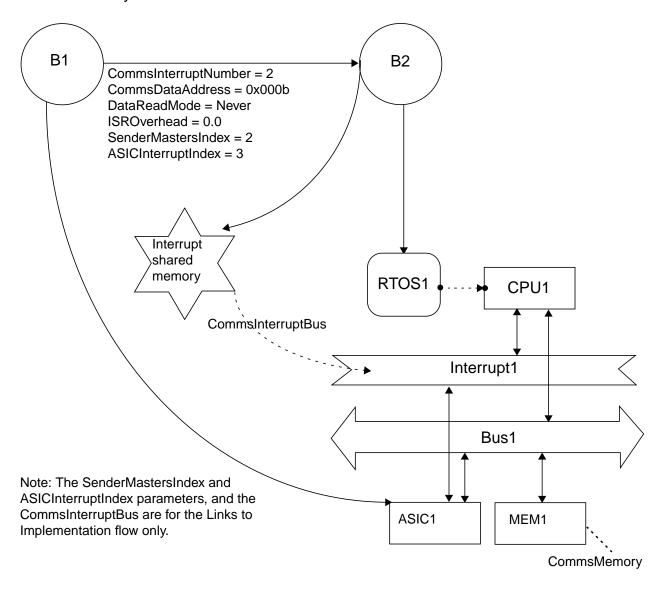

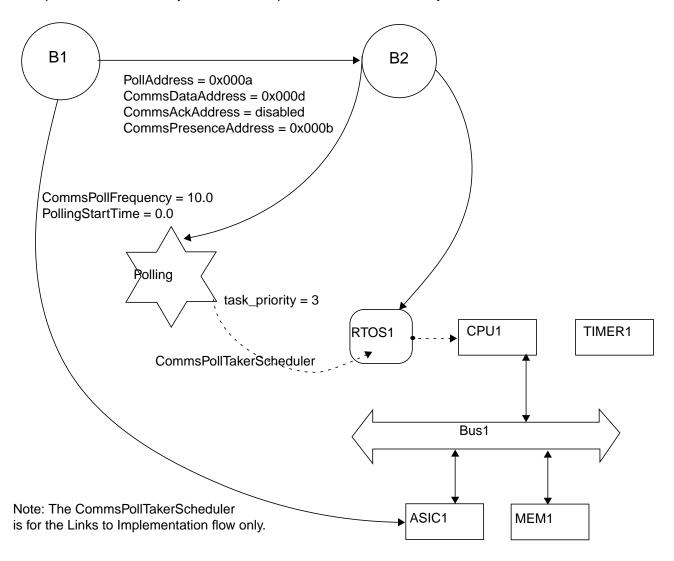

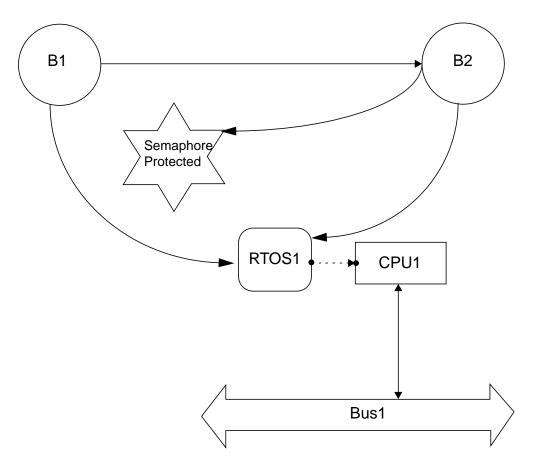

Behaviors 5 and 3 run first. Once they complete, scheduler B is ready to run. All of the behaviors assigned to scheduler B run in the order in which they were received by scheduler B. Once these three tasks complete, behavior 4 runs.